Highly Conductive Shallow Junction Formation

a technology of shallow junctions and high conductive conductivity, which is applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve the problems of increasing reverse bias leakage, affecting the effect of reverse bias, and reducing the diffusion rate of the devi

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

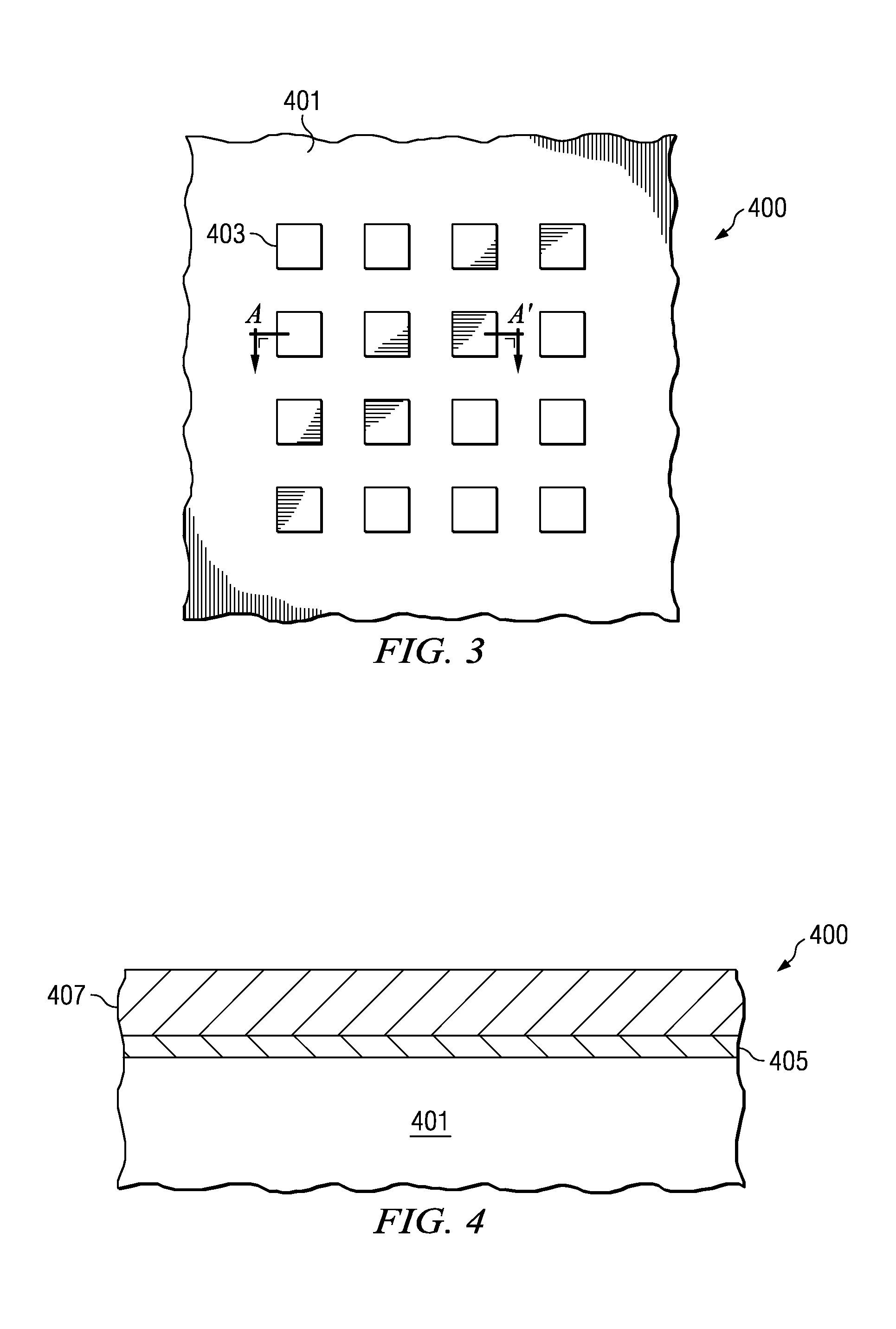

[0019]The present invention will now be described with reference to the attached drawings, wherein like reference numerals are used to refer to like elements throughout. Exemplary processes comprising series of acts and events are provided. The present invention is not limited by the ordering of the acts and events in these examples as some acts may occur in different orders and / or concurrently with other acts or events. In addition, not all illustrated acts or events are required to implement a methodology in accordance with the present invention.

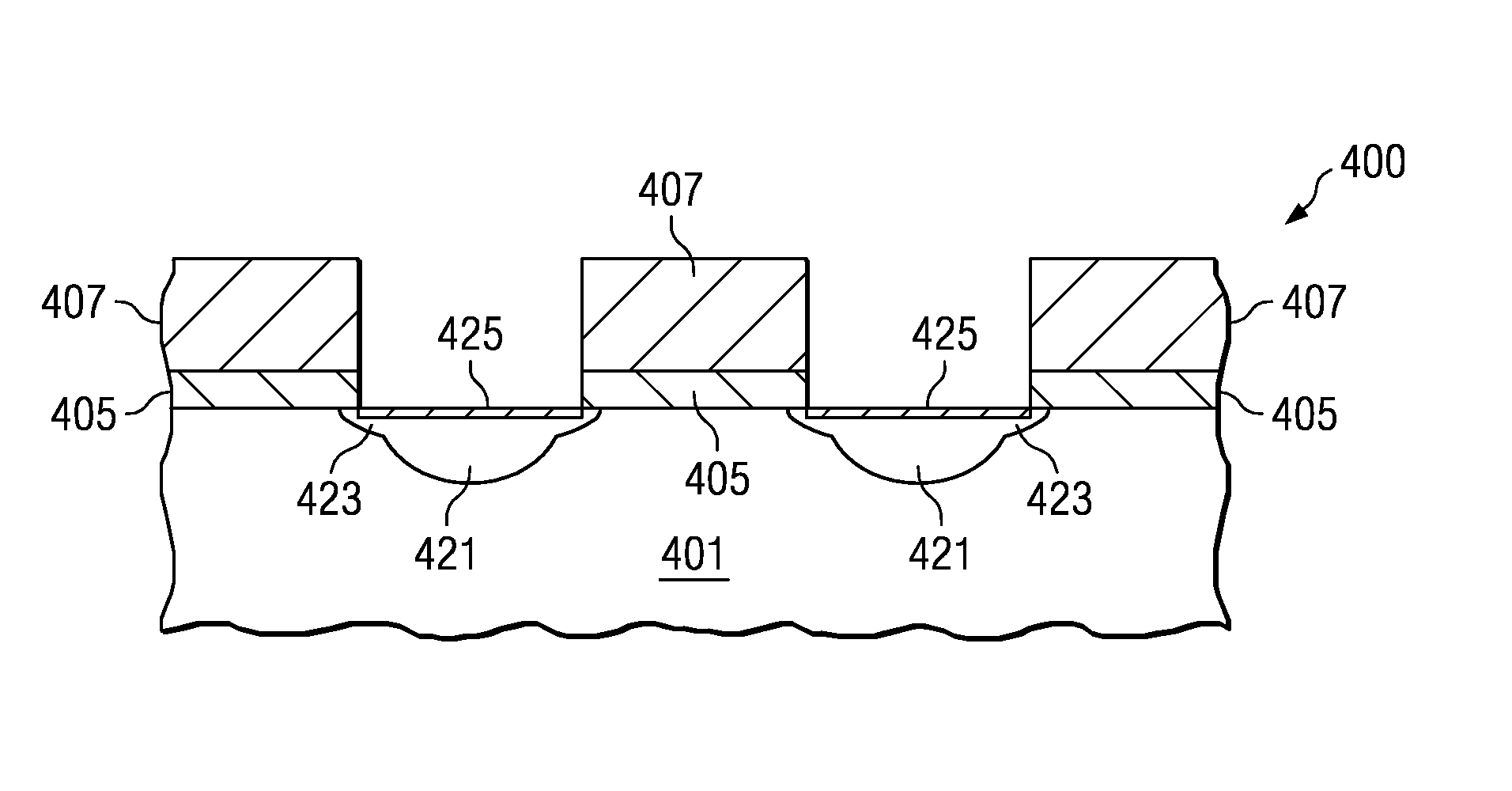

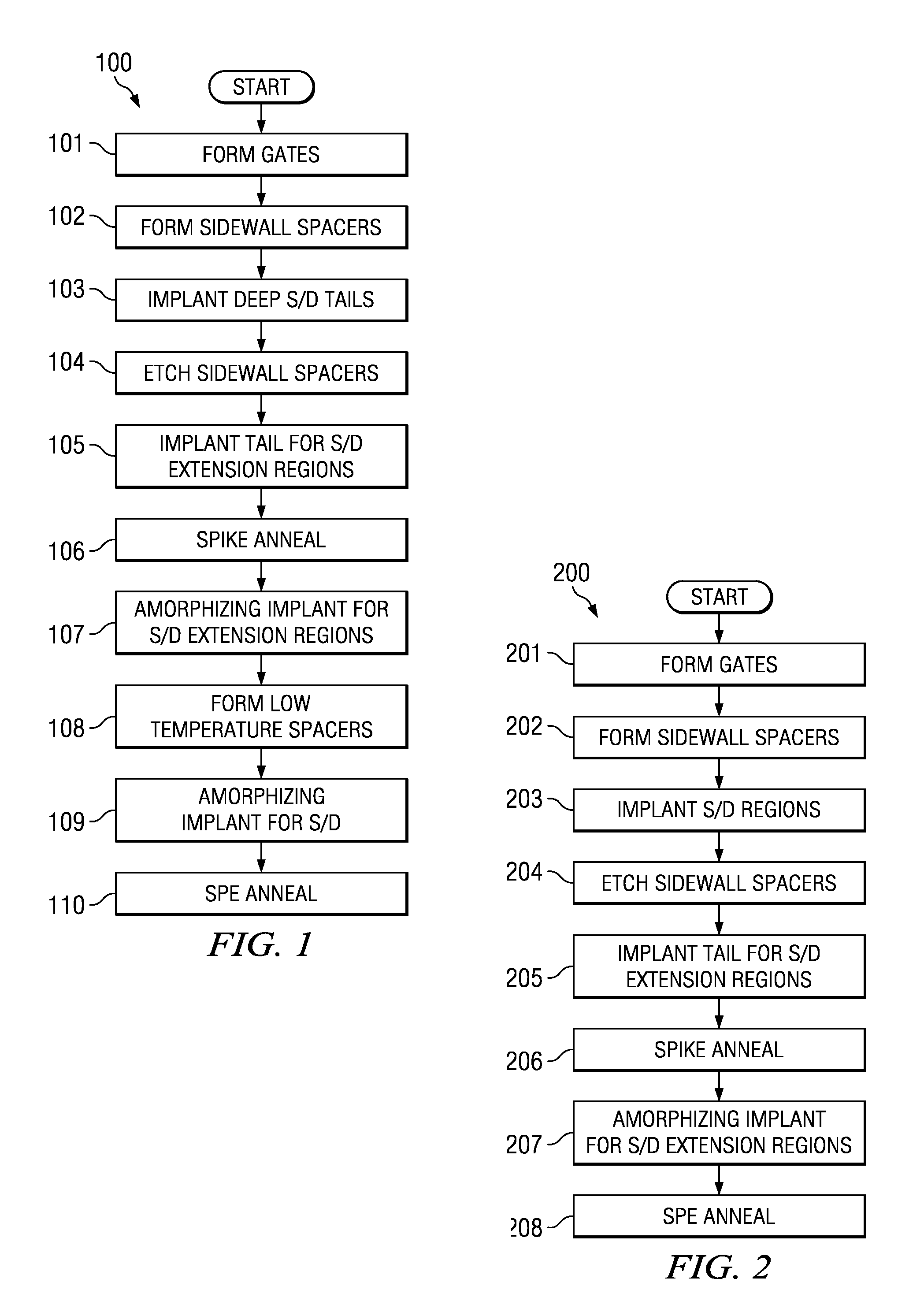

[0020]FIG. 1 illustrates an exemplary process 100 for forming a P-N junction within a semiconductor substrate according to one aspect of the present invention. The process 100 includes gate formation 101, forming sidewall spacers 102, forming deep source / drain implants 103, and etching away the sidewall spacer 104. The process further includes forming a source / drain extension region tail implant 105, annealing to activate the dopants 106, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com