Methods for forming dense dielectric layer over porous dielectrics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

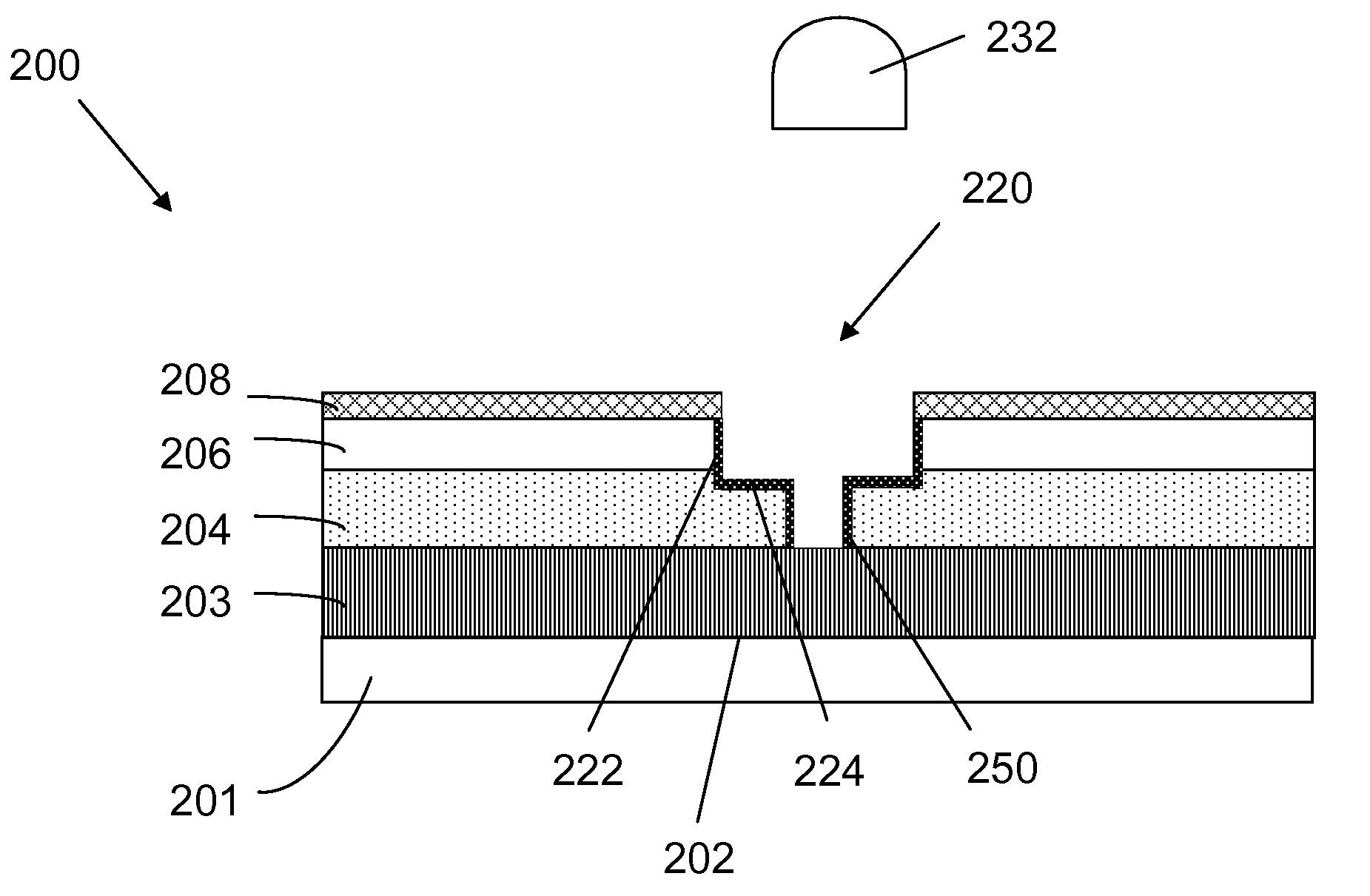

[0018]Turning to the drawings, FIG. 1 shows a preliminary structure 100 on a wafer 101, to which a method according to embodiments of the disclosure will be applied. Although a single structure 100 is shown for the sake of clarity, it should be appreciated that wafer 101 may include multiple structures. In this embodiment, an interconnect wiring network (not shown) is formed using a dual damascene (DD) process. In the DD process, an inter-metal dielectric (IMD or ILD), shown as two layers 104, 106, is coated on a substrate 103. Layer 104 (e.g., a via level dielectric) and layer 106 (e.g., a line level dielectric) are shown separately for clarity of the process flow description. Layers 104, 106 may be made of the same or different dielectric materials, and in the former case, applied as a single monolithic layer. A hard mask layer or a layered stack 108 is optionally employed to facilitate etch selectivity and to serve as a polish stop. Layers 104, 106 may be porous ultra low dielect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com