Semiconductor device and method for making the same

a technology of semiconductor devices and semiconductors, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve problems such as framing being susceptible to heat, memory operation becoming unstable, and memory no longer operating

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Preferred embodiments of the present invention will be described in specific details, referring to the accompanying drawings.

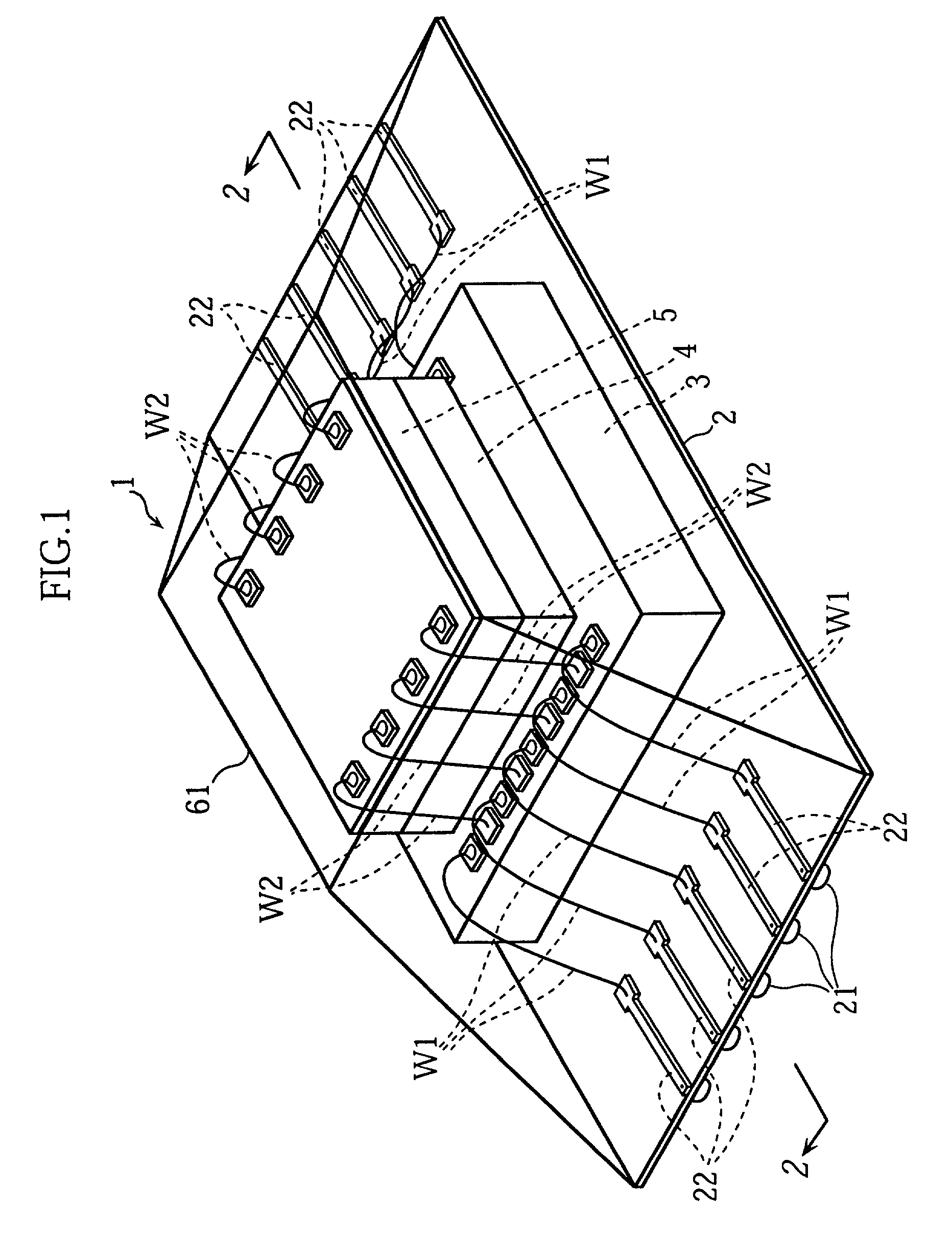

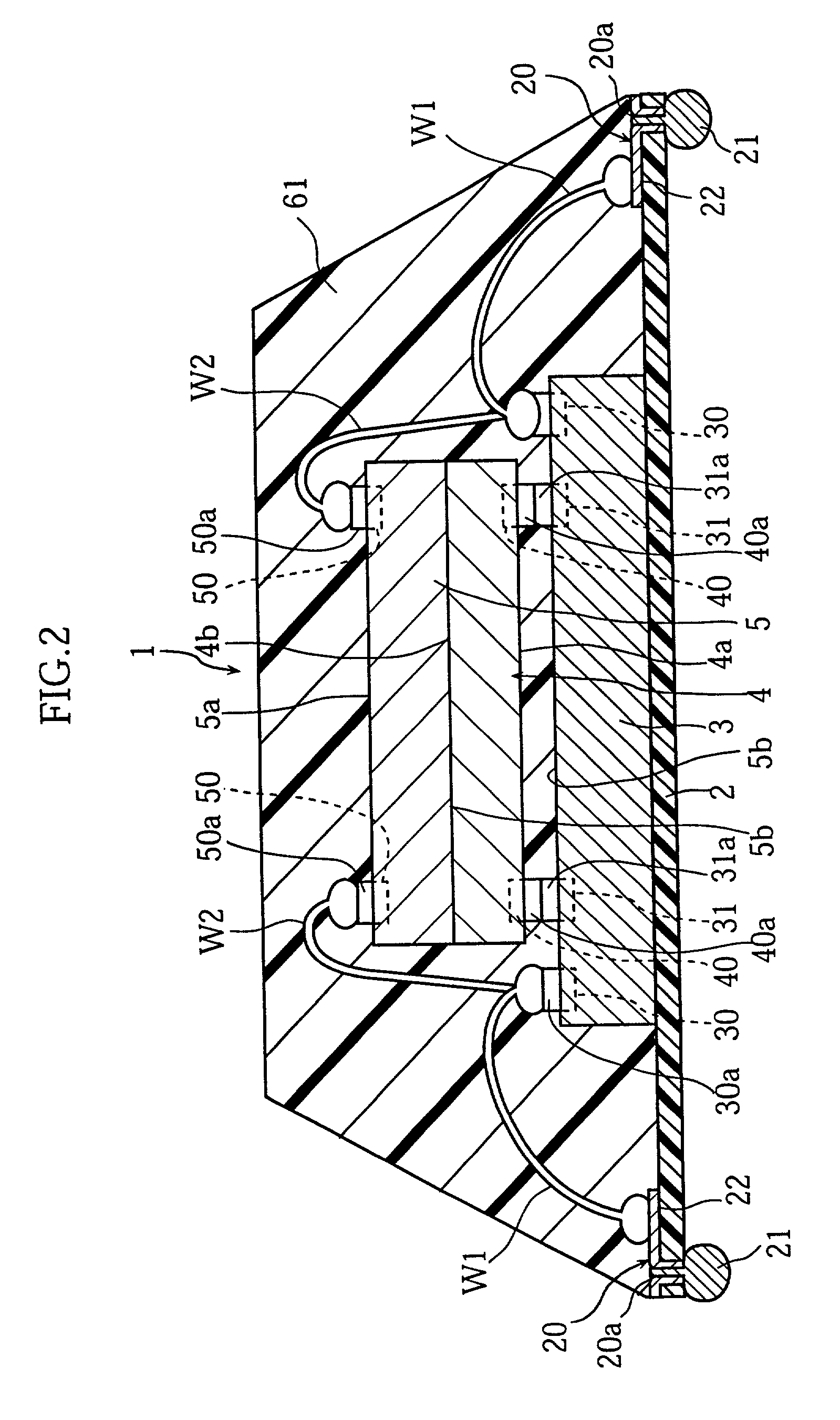

[0054] FIG. 1 is an overall perspective view of a semiconductor device as an embodiment of the present invention. FIG. 2 is a sectional view taken in lines 2-2 in FIG. 1.

[0055] As shown in FIGS. 1 and 2, a semiconductor device 1 generally comprises a film substrate 2 made of a polyimide resin for example, a first semiconductor chip 3 mounted to the film substrate 2, a second semiconductor chip 4 electrically connected with the first semiconductor chip 3, and a third semiconductor chip 5 mounted onto the second semiconductor chip 4.

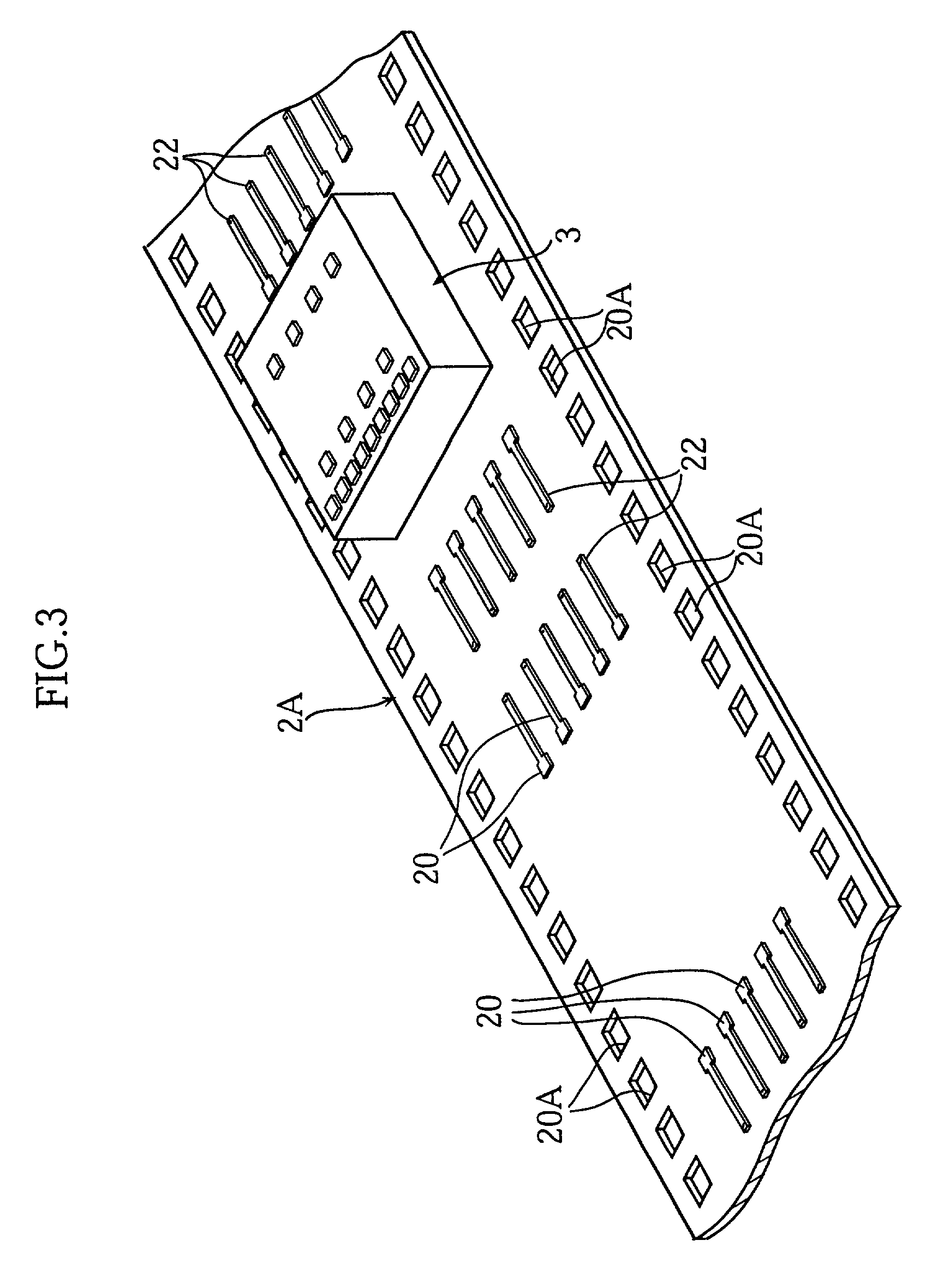

[0056] The film substrate 2 has two end portions each formed with a plurality of through-holes 20a. At each of these through-holes 20a, a corresponding terminal 20 is formed. Each terminal 20 is provided with a thin-film terminal portion 22 formed on an upper surface of the film substrate 2, and a ball terminal portion 21 form...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com