Integrated circuit or discrete component flat bump package technics and its package structure

A flat bump type, discrete component technology, applied in electrical components, circuits, electrical solid devices, etc., can solve problems such as ability to affect solderability, poor contact, contact cracking, etc., to achieve product quality assurance, reliability assurance , to ensure the effect of stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The integrated circuit or discrete component planar bump type packaging process of the present invention consists of the following procedures:

[0056] 1) Substrate - see figure 1 , take a piece of metal substrate 1 with an appropriate thickness. The material of the metal substrate 1 can be changed according to the functions and characteristics of the chip, for example: nickel-iron alloy, pure copper or copper alloy.

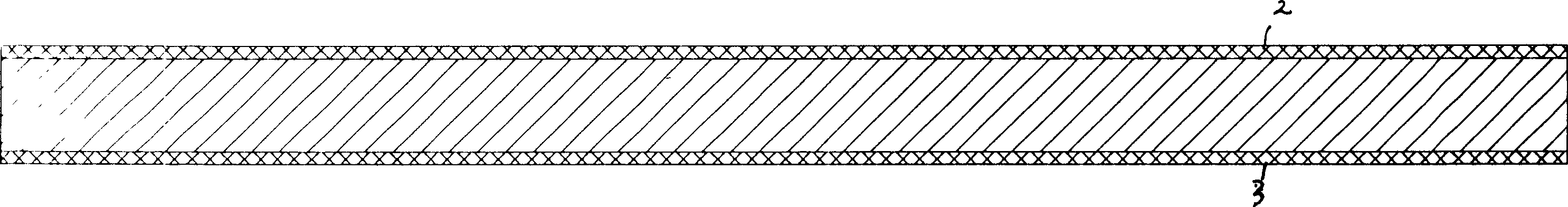

[0057] 2) Applied dry film - see figure 2 , affix dry film layers 2 and 3 on both sides of the metal substrate to protect the subsequent etching process.

[0058] 3) Remove part of the dry film - see image 3 , correspondingly remove part of the dry film on both sides of the metal substrate 1, and prepare to form base islands and pins on the metal substrate 1, in order to expose the area on the substrate that needs to be plated with activating substances later,

[0059] 4) Plating activating substances - see Figure 4 , both sides of the base islan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com