Semiconductor device and method of fabricating the same

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as damaging the surface of semiconductor layers, increasing the process of removing polymers, and uneven contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

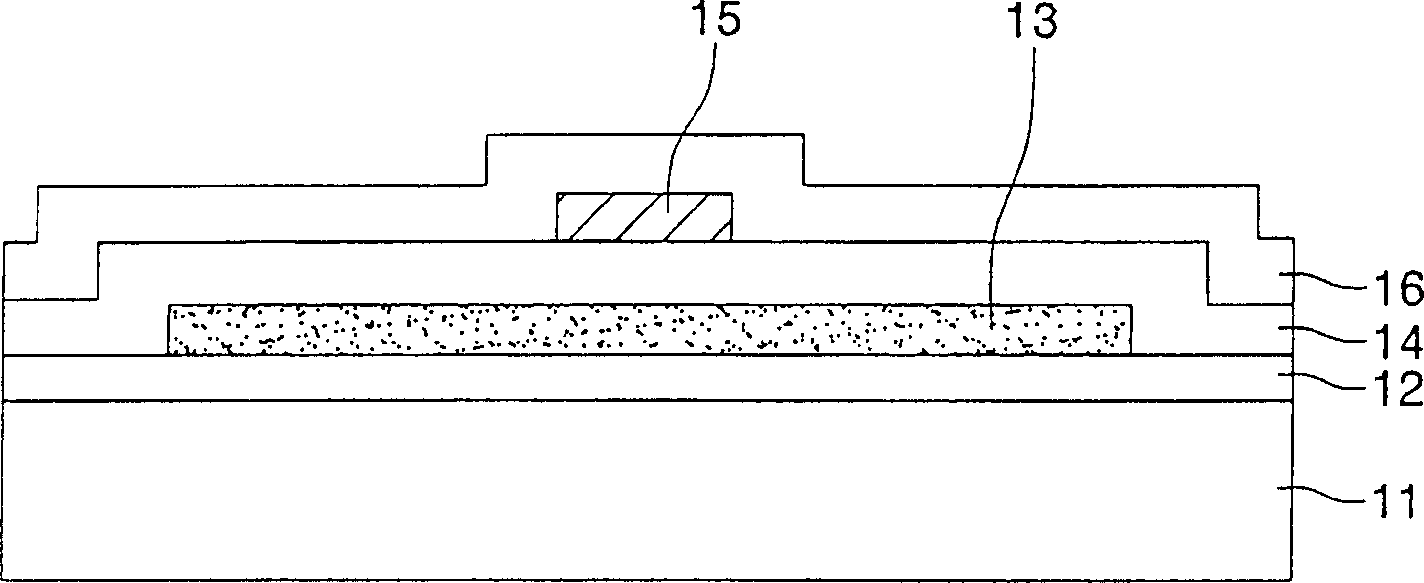

[0035] Figures 3A-3E is a cross-sectional view showing a method of forming a contact hole according to an embodiment of the present invention and a process of using the contact hole.

[0036] first, Figure 3A It is a cross-sectional view of the process of forming a buffer layer, a semiconductor layer, a gate insulating layer, a gate electrode and an interlayer dielectric on a substrate. Such as Figure 3A As shown, a buffer layer 102 is formed on an insulating substrate 101 such as plastic or glass. The buffer layer 102 functions to prevent the diffusion of water vapor or impurities generated from the insulating substrate, or to facilitate the crystallization of the semiconductor layer by adjusting the heat conduction rate when crystallization is performed.

[0037] Next, an amorphous silicon layer is formed on the buffer layer 102 , and then the amorphous silicon layer is crystallized into a polycrystalline silicon layer or a single crystal silicon layer, which is patter...

no. 2 example

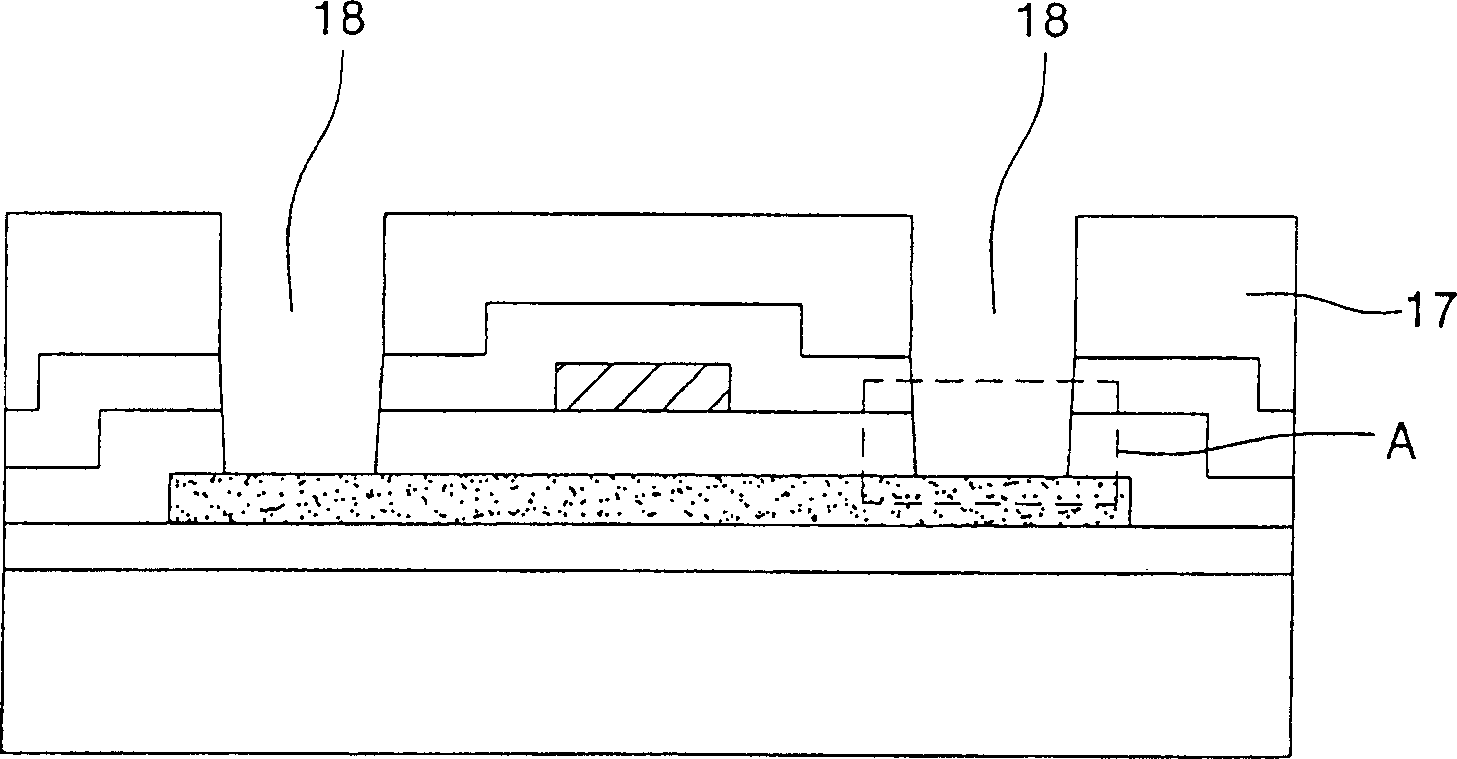

[0053] Figures 4A-4G are sectional views showing a method of forming a contact hole according to another embodiment of the present invention, and a sectional view and a sectional photograph of a process using the contact hole.

[0054] first, Figure 4A is a sectional view illustrating the steps of forming a buffer layer, a semiconductor layer, a gate insulating layer, a gate electrode, and an interlayer dielectric on a substrate. Such as Figure 4A As shown, a buffer layer 152 is formed on an insulating substrate 151 such as plastic or glass. The buffer layer 152 functions to prevent the diffusion of water vapor or impurities generated from the insulating substrate, or to facilitate the crystallization of the semiconductor layer by adjusting the heat conduction rate when crystallization is performed.

[0055] Next, an amorphous silicon layer is formed on the buffer layer 152 , and then the amorphous silicon layer is crystallized to form a polycrystalline silicon layer or ...

no. 3 example

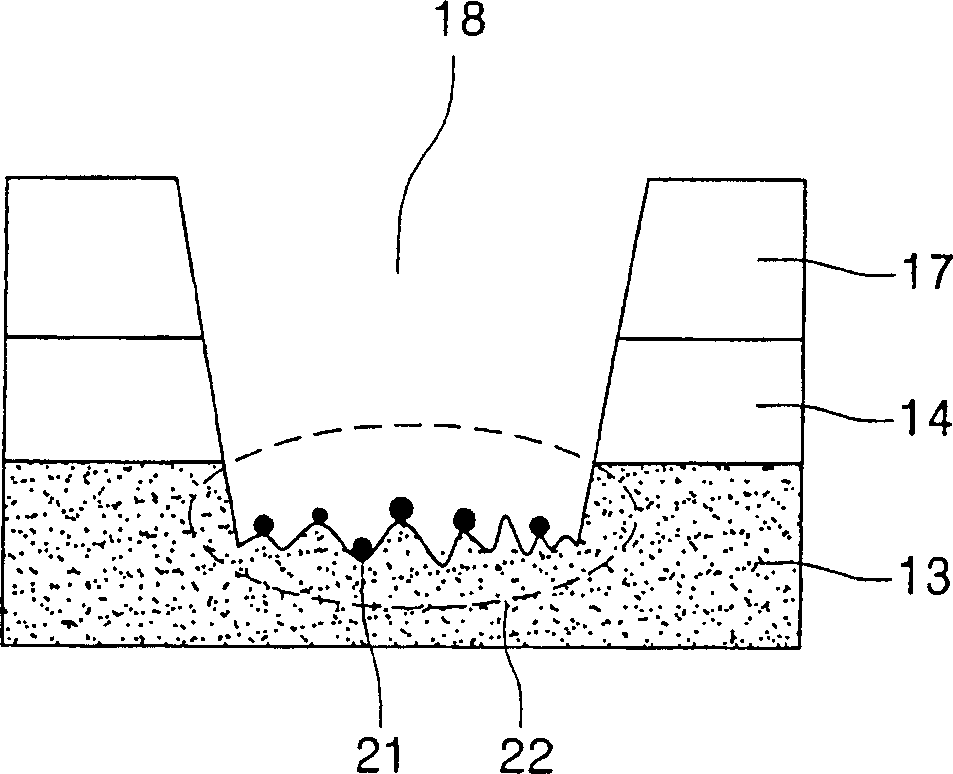

[0081] Figures 5A-5E is a sectional view showing a method of forming a through hole and a process of using the through hole according to another embodiment of the present invention.

[0082] first, Figure 5A is a cross-sectional view of the steps of forming a buffer layer, a semiconductor layer, a gate insulating layer, a gate electrode, an interlayer dielectric, and source and drain electrodes on a substrate. Such as Figure 5A As shown, a buffer layer 202 is formed on an insulating substrate 201 such as plastic or glass.

[0083] Next, an amorphous silicon layer is formed on the buffer layer 202 , and then the amorphous silicon layer is crystallized into a polycrystalline silicon layer or a single crystal silicon layer and patterned to form the semiconductor layer 203 . In this case, a CVD method or a PVD method may be used for the amorphous silicon layer.

[0084] Next, a gate insulating layer 204 is formed over the entire surface of the substrate in which the semicon...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Cone angle | aaaaa | aaaaa |

| Cone angle | aaaaa | aaaaa |

| Cone angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com