Polysilicon film transistor of liquid crystal display device and its mfg. method

A polysilicon, intermediate layer technology, applied in transistors, semiconductor/solid-state device manufacturing, instruments, etc., can solve the problems of increased production cost and process deviation, and achieve the effect of simplifying the manufacturing method and preventing surface damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

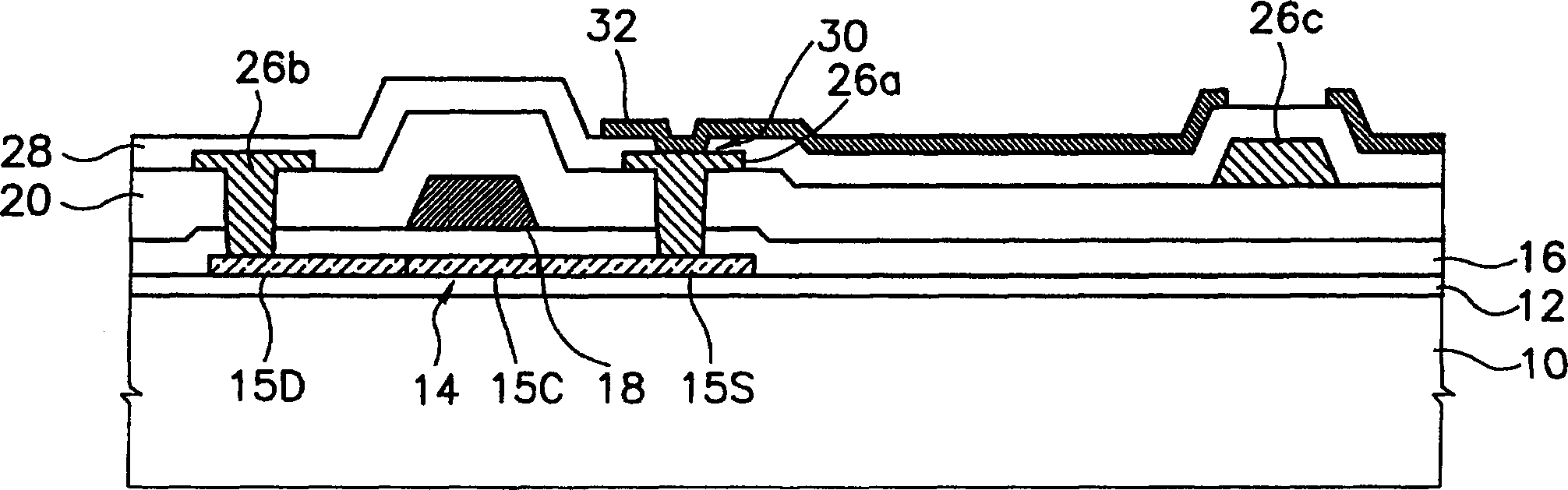

[0053] figure 2 A cross-sectional view of a polysilicon TFT according to a first embodiment of the present invention is shown.

[0054] refer to figure 2 , on a transparent substrate 100 made of a transparent insulating material such as glass, quartz or sapphire, a barrier layer 102 is formed. A polysilicon effective pattern 104 is formed on the barrier layer 102 . The effective pattern 104 includes a lower electrode 105T integrally formed with the effective pattern.

[0055] On the effective pattern 104 and the barrier layer 102, a gate insulating layer 106 made of silicon nitride or silicon oxide is formed. A gate electrode 108a is formed on the gate insulating layer 106 across the effective pattern 104 to define source / gate regions 105S and 105D. That is, a part of the effective pattern 104 overlapped by the gate electrode 108a is used as the channel region 105C of the TFT, and one side of the effective pattern 104 divided with respect to the channel region 105C locat...

Embodiment 2

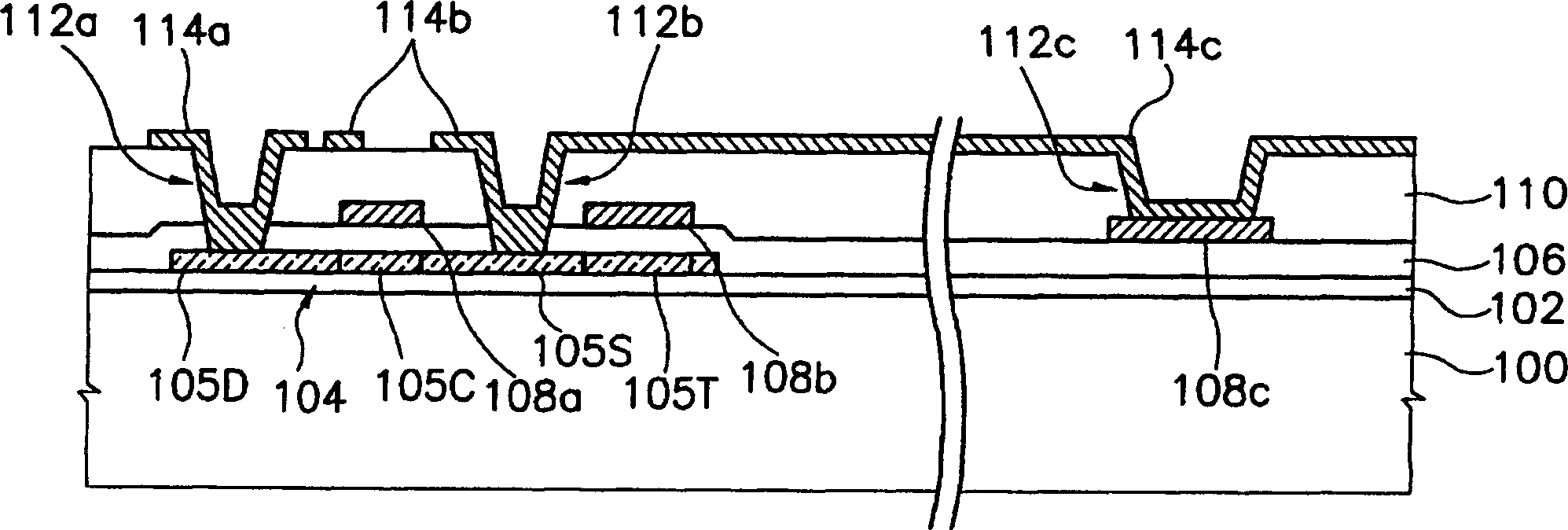

[0081] Figure 6 A cross-sectional view of a polysilicon TFT according to a second embodiment of the present invention is shown.

[0082] refer to Figure 6 , after forming the data line 114a, the pixel electrode 114b and the conductive pattern 114c (using the fifth mask) for connecting the gate pad in the same manner as in Embodiment 1, such as silicon nitride (SiN x ) is deposited on the entire surface of the synthetic material to form a passivation layer 116 . Then, the passivation layer 116 on the conductive pattern 114c is etched using a photolithography process to expose the conductive pattern 114c (using a sixth mask).

[0083] If the passivation layer is formed as described above, compared with Embodiment 1, the number of masks is increased to six. However, it is advantageous to prevent the data line 114a and the pixel electrode 114b from being contaminated, and to protect the patterning. Preferably, the passivation layer 116 has a desired thickness so that an elec...

Embodiment 3

[0085] Figure 7A to Figure 7D is a cross-sectional view illustrating a method of manufacturing a polysilicon TFT according to a third embodiment of the present invention.

[0086] refer to Figure 7A , on the transparent substrate 100, in a manner similar to that in Embodiment 1, a barrier layer 102, an effective pattern 104, a gate insulating layer 106, gate lines and capacitor lines 108b are formed. The gate line includes a gate line formed in the display area, a gate electrode 108a as a part of the gate line, and a gate pad 108c formed in a pad area located outside the display area. During the formation of the gate lines, signal transmission lines (not shown) spaced a predetermined distance away from the gate lines and extending in a direction perpendicular to the gate lines are also formed together with the gate lines.

[0087] Then, an organic insulating material is deposited to a thickness of several thousand Å on the gate line, the capacitor wire 108 b and the gate i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com