Crystal covered chip and crystal covered package substrate

A technology for packaging substrates and flip chips, which is applied to electrical components, electrical solid-state devices, circuits, etc., can solve the problems of increasing the length of the signal transmission path, reducing the electrical performance of the chip 110, and increasing the line length of the chip 110.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

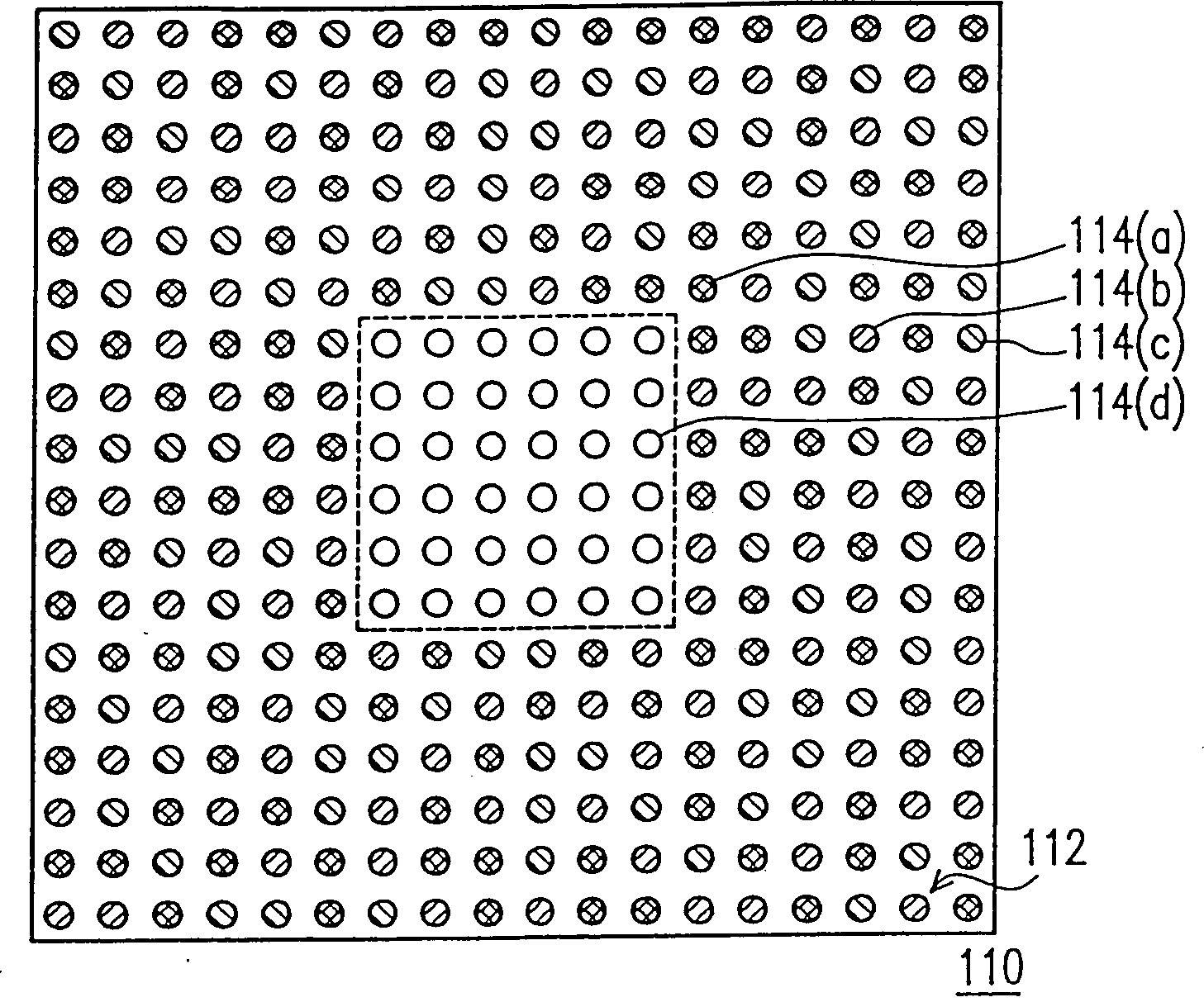

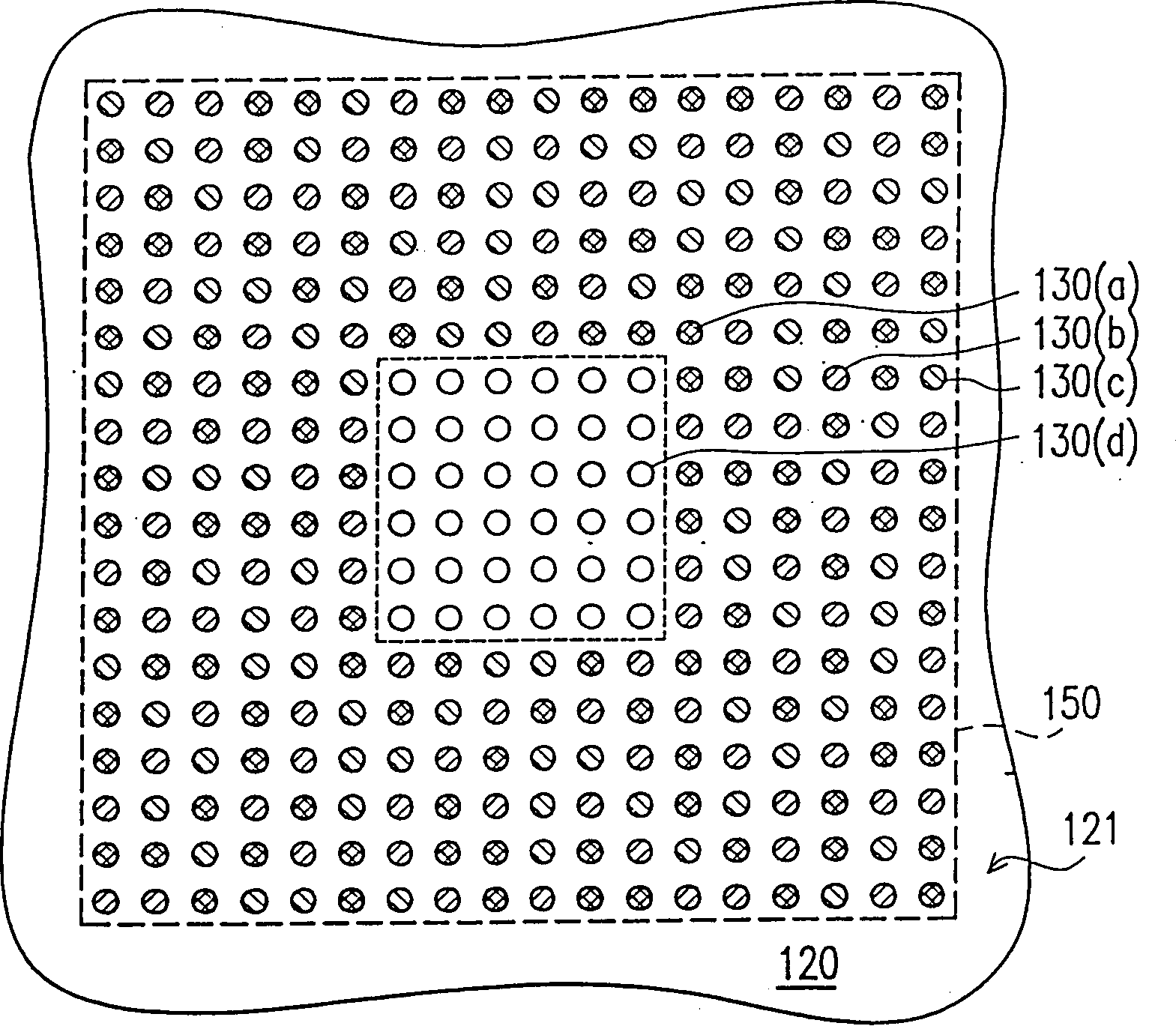

[0044] Please refer to Figure 3A , which is a bottom view of a chip in a preferred embodiment of the present invention. The active surface 212 of the chip 210 is provided with a plurality of bonding pads 214 (such as component numbers 214 a , 214 b , 214 c , 214 d . . . ) in a matrix, forming a plurality of bonding pad rings 215 . In addition, according to different functions, the pads 214 can also be divided into signal pads 214a, power pads 214b, ground pads 214c, and core power / ground pads 214d, wherein the signal pads 214a, power pads 214b and ground pads The pads 214c are centered on the core power / ground pads 214 and distributed around the core power / ground pads 214d. It should be noted that, for a signal pad ring composed of a plurality of pads 214 (such as the second pad ring 215b, the third pad ring 215c and the sixth pad ring 215f), the pads 214 have 100% More than 50% are signal pads 214a, and preferably, more than 90% of the pads 214 of the signal pad ring are s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com