Double-channel MOSFET semiconductor device

A dual-channel, semiconductor technology, used in semiconductor devices, electrical components, circuits, etc., to achieve the effects of reducing on-resistance, smoothing the concentration of electric fields, and increasing density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

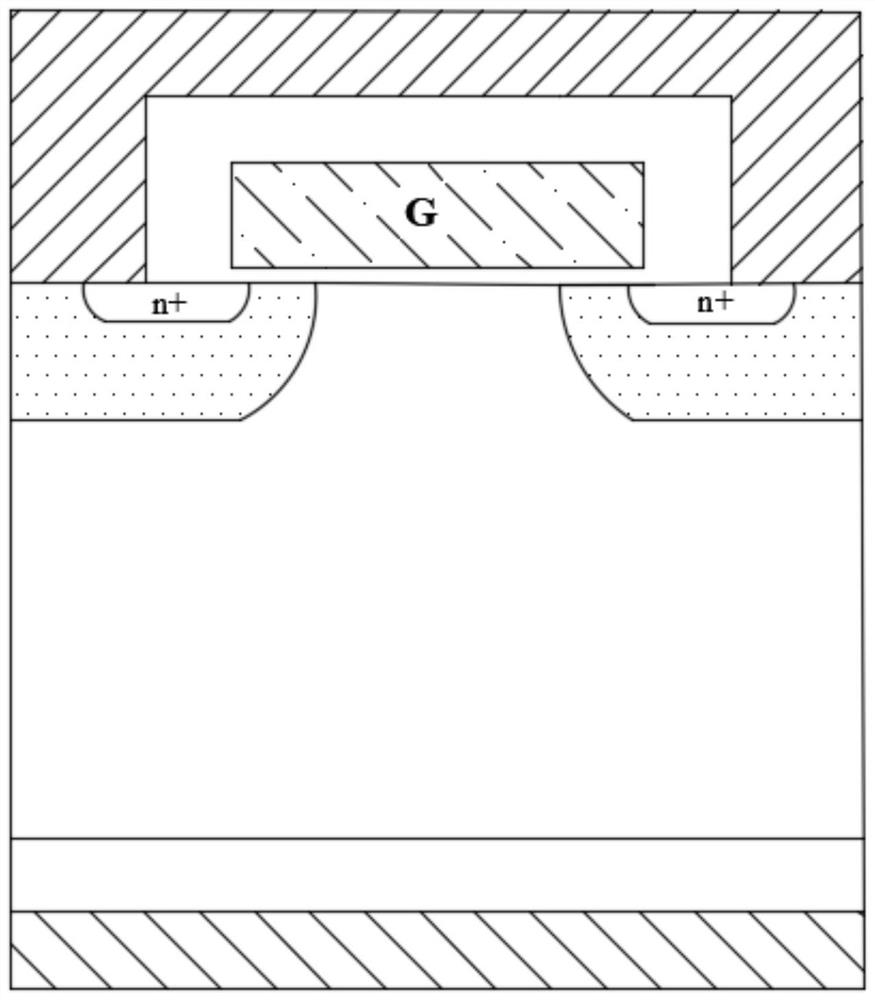

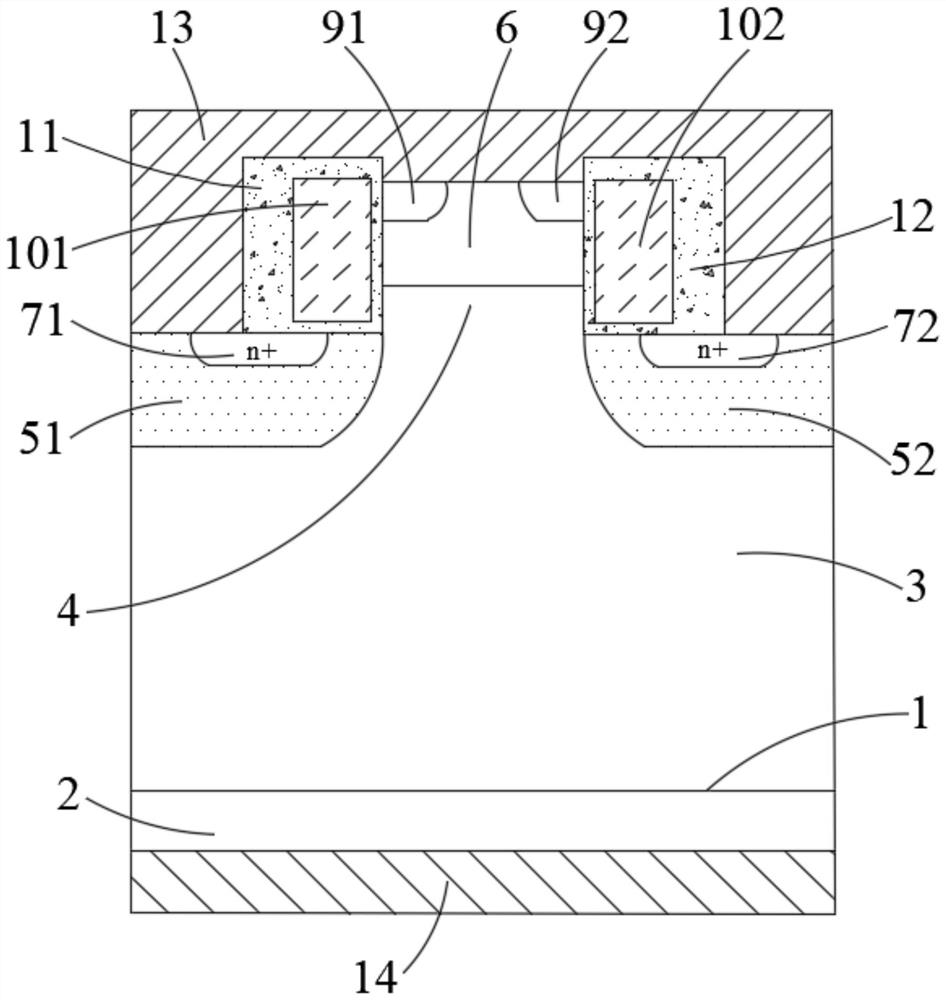

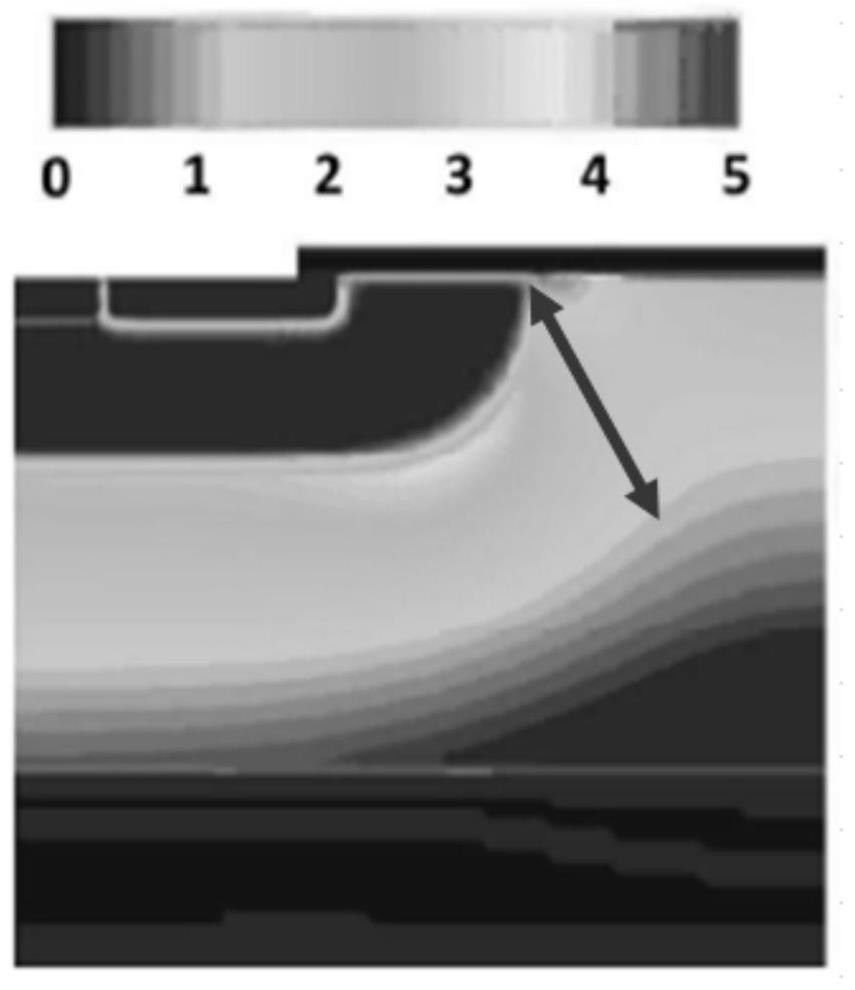

[0019] Embodiment 1: A kind of dual-channel MOSFET semiconductor device, comprising: the heavily doped N-type drain layer 2 located at the lower part of the silicon wafer 1 and the N-type doped epitaxial layer 3 located at the middle and upper part of the silicon wafer 1, the N-type The central region 8 of the doped epitaxial layer 3 has a raised portion 4 extending upward, and the upper part of the N-type doped epitaxial layer 3 and the two sides of the central region 8 respectively have a P-type left base region 51 and a P-type right base region. region 52, the upper part of the raised portion 4 has a P-type upper base region 6, and the upper parts of the P-type left base region 51 and the P-type right base region 52 respectively have a heavily doped N-type left source region 71 and The heavily doped N-type right source region 72, the upper part of the P-type upper base region 6 and the left and right sides are alternately provided with a heavily doped N-type upper left sourc...

Embodiment 2

[0024] Embodiment 2: A kind of dual-channel MOSFET semiconductor device, comprising: the heavily doped N-type drain layer 2 located at the lower part of the silicon wafer 1 and the N-type doped epitaxial layer 3 located at the middle and upper part of the silicon wafer 1, the N-type The central region 8 of the doped epitaxial layer 3 has a raised portion 4 extending upward, and the upper part of the N-type doped epitaxial layer 3 and the two sides of the central region 8 respectively have a P-type left base region 51 and a P-type right base region. region 52, the upper part of the raised portion 4 has a P-type upper base region 6, and the upper parts of the P-type left base region 51 and the P-type right base region 52 respectively have a heavily doped N-type left source region 71 and The heavily doped N-type right source region 72, the upper part of the P-type upper base region 6 and the left and right sides are alternately provided with a heavily doped N-type upper left sourc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com