Stacked chip and test method of stacked chip

A test method and chip technology, which can be used in electronic circuit testing, measuring device casings, etc., can solve problems such as large resource consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

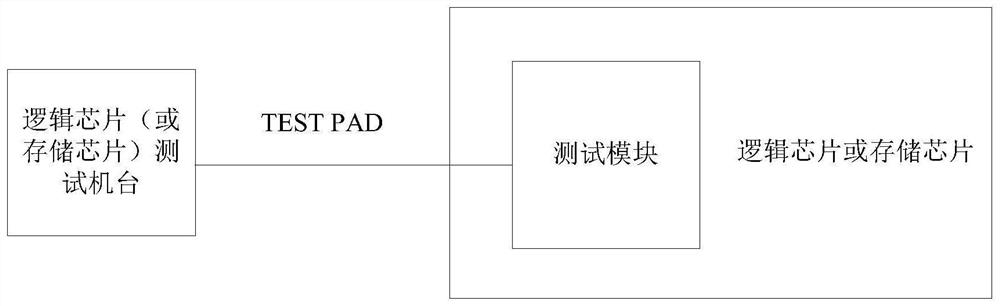

Problems solved by technology

Method used

Image

Examples

Embodiment 1

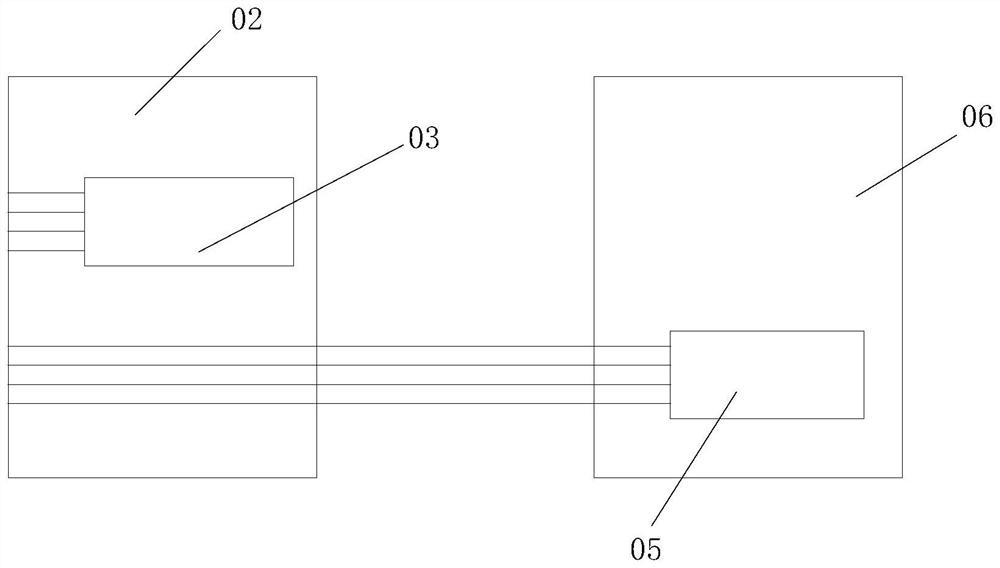

[0074] In a specific embodiment of the present application, such as Figure 4 As shown, the stacked chip system includes: a testing machine 01, a first chip 02, and a second chip 06, wherein the first chip 02 is a logic chip, the second chip 06 is a memory chip, and the logic chip includes two test modules, namely the first test module 03 and the second test module 05, namely the BIST test module and the DFT test module, and a first multiplexer 07, namely the MUX module, the DFT test module in the logic chip and the storage The chips are electrically connected, and the test machine 01 can test the memory chip through the external interface of the DFT test module. The specific test process is as follows: the test machine 01 sends out two sets of test signals, and the MUX module judges according to the received test signals. The test module corresponding to the test signal is obtained, and one group of test signals is input to the BIST test module (ie the first test module 03) i...

Embodiment 2

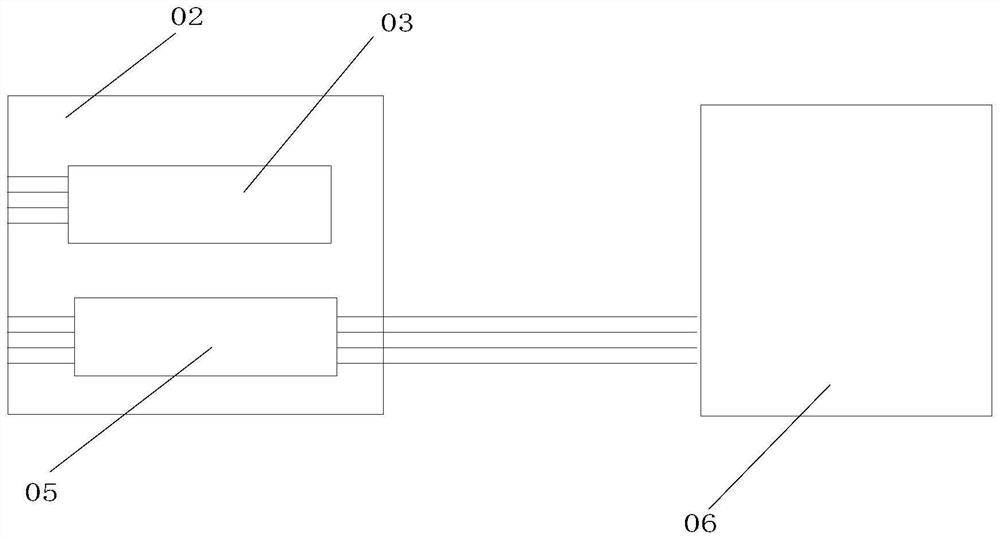

[0076] In another specific embodiment of the present application, such as Figure 5 As shown, the stacked chip system includes: a test station 01 , a first chip 02 , a second chip 06 , a third chip 09 , a first multiplexer 07 and a second multiplexer 08 , wherein, the first chip 02 integrates three test modules, namely the first test module 03 , the second test module 05 and the third test module 10 , that is, the first test module 03 is used to test the first chip 02 , the second test module 05 is used to test the second chip 06, the third test module 10 is used to test the third chip 09, the second multiplexer 08 is located in the first chip 02, the second multiplexer One end of the device 08 is electrically connected to the second test module 05 and the third test module 10 respectively, and the other end of the second multiplexer 08 is electrically connected to the second chip 06 and the third chip 09 respectively. The specific test process is as follows: For the test The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com