LDMOS device manufacturing method, LDMOS device and terminal equipment

A manufacturing method and device technology, which can be used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as inability to generate an electron accumulation layer.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example ;

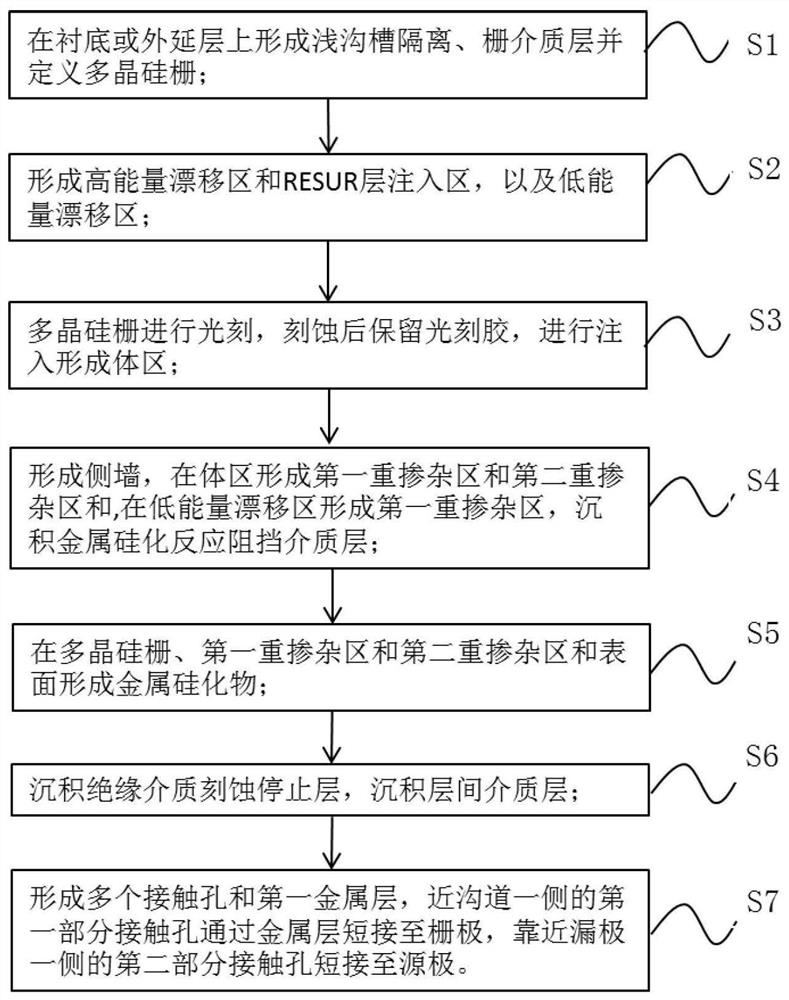

[0048] Such as figure 2 As shown, the present invention provides a kind of LDMOS device manufacturing method, comprises the following steps:

[0049] S1, forming shallow trench isolation 102 on the substrate or epitaxial layer 101, then forming a gate dielectric layer 103, depositing and forming a polysilicon layer, and etching to define a polysilicon gate 104 at the same time;

[0050] S2, coating the photoresist 501 and opening the photoresist in the LDMOS region, performing drift region and RESURF implantation, forming a high-energy drift region with uneven ion concentration distribution in the lateral direction, a RESUR layer implantation region 105, and a low-energy drift region 106 ;

[0051] S3, performing photolithography on the defined polysilicon gate 104, retaining the photoresist after etching, and performing implantation to form the body region 107;

[0052] S4, form sidewalls 108 on both sides of the polysilicon gate 104, perform highly doped implantation in t...

no. 2 example ;

[0057] The invention provides a method for manufacturing an N-LDMOS device, comprising the following steps:

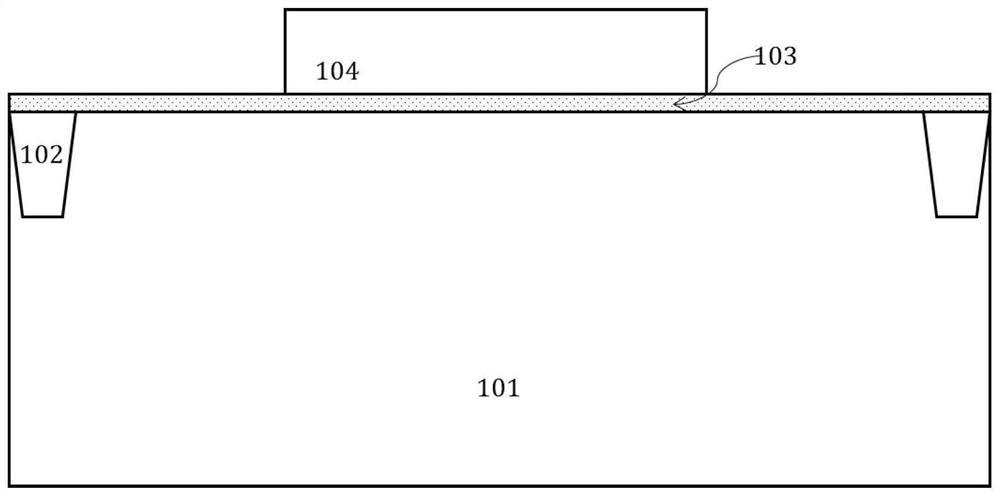

[0058] S1, such as image 3 As shown, shallow trench isolation 102 is formed on 101—P-type substrate / P-type epitaxial layer 101, then thermally oxidized to form a gate dielectric layer 103, deposited to form a polysilicon layer, and etched to define a polysilicon gate 104 at the same time;

[0059] S2, such as Figure 4 As shown, the photoresist 501 is coated and the photoresist in the LDMOS region is opened, and the drift region and RESURFP type implantation are performed to form a high-energy drift region and a RESUR layer implantation region 105 with uneven ion concentration distribution in the lateral direction, and a low-energy drift region. District 106;

[0060] Due to the existence of the defined polysilicon gate 104, high-energy (>80KeV) drift region and RESURF (>300KeV) implants directly pass through the polysilicon gate 104 and enter Silicon, while low-ene...

no. 3 example ;

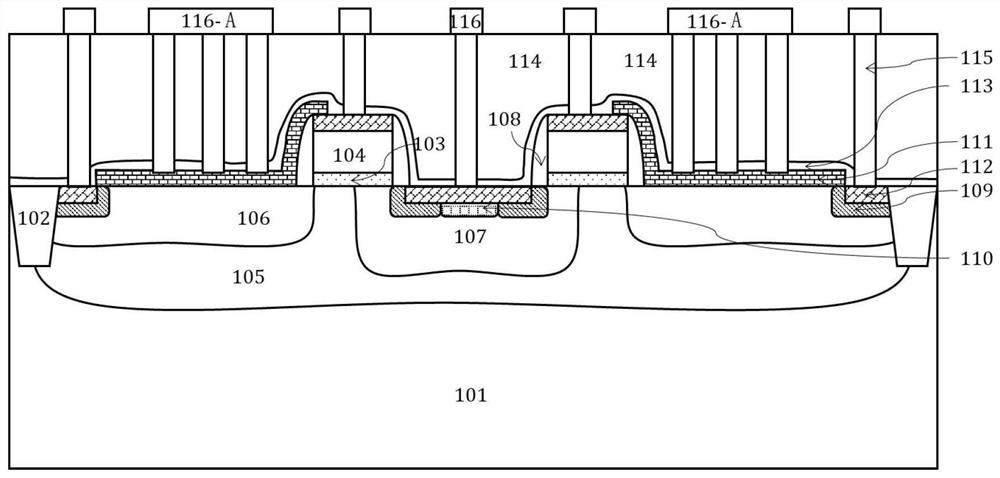

[0067] Such as Figure 7 As shown, the present invention provides an LDMOS device manufactured by the method for manufacturing an LDMOS device described in any one of the first embodiment or the second embodiment above, including:

[0068] Shallow trench isolation 102 formed in the substrate or epitaxial layer 101;

[0069] High-energy drift region and RESUR layer implant region 105 formed on the substrate or epitaxial layer 101 between shallow trench isolations 102;

[0070] Low energy drift region 106, which is formed on the upper part of substrate or epitaxial layer 101 between shallow trench isolation 102 and body region 107, and adjacent to shallow trench isolation 102;

[0071] a body region 107 formed on top of the substrate or epitaxial layer 101 between the low energy drift regions 106;

[0072] The first heavily doped region 109 is formed on the upper part of the low-energy drift region 106 and the upper part of the body region 107;

[0073] a second heavily doped...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com