Transverse SCR anti-static structure for SOI process and preparation method thereof

An anti-static, lateral technology, applied in circuits, electrical components, electrical solid-state devices, etc., can solve problems such as inability to meet miniaturization requirements, SCR performance impact, and inability to freely choose doping concentration and doping area size.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0026] Such as figure 1 As shown, the traditional SCR antistatic structure mostly adopts a lateral SCR structure, forming N well and P well regions respectively, and then forming N+ and P+ regions by pre-deposition. This preparation method has to consider factors such as lateral diffusion and related The formation of the region depends on the oxidation diffusion preparation process of the circuit. The chip area that needs to be used is relatively large, and the SCR structural parameters or impurity concentration cannot be adjusted under the condition of ensuring the circuit performance, and the process limitation is relatively large.

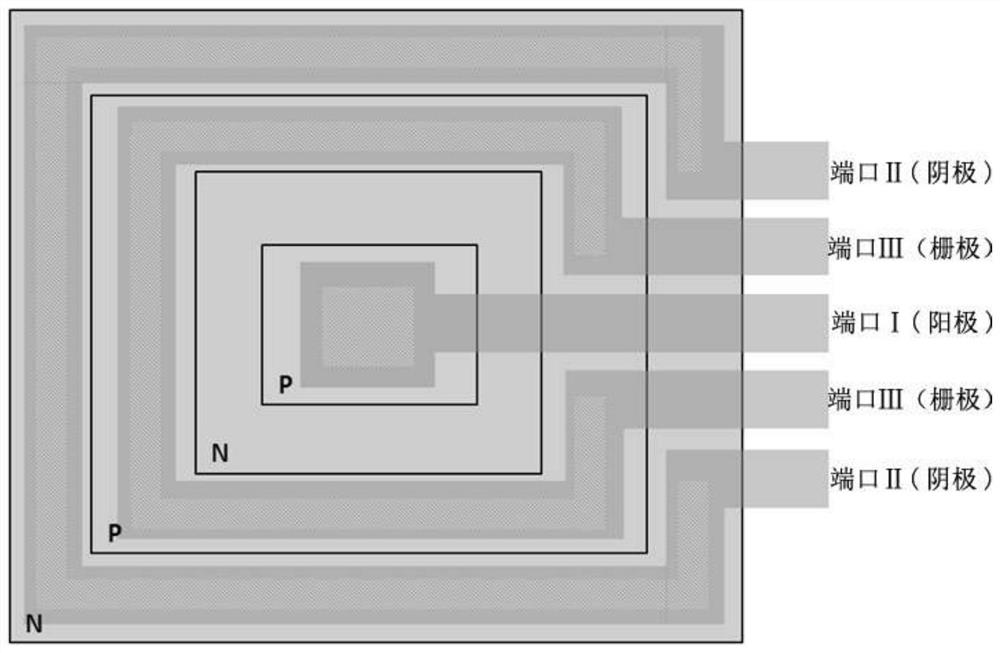

[0027] Such as figure 2 As shown, the antistatic structure of the SCR of the present invention is distributed in a horizontal PNPN, and the whole is divided into 4 regions, of which the innermost is the P regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com