Programming and read bias and access scheme to improve data throughput of 2-stack 3D PCM memories

A memory and bias technology, applied in static memory, read-only memory, digital memory information, etc., can solve the problems of high cost, difficult plane processing and manufacturing technology, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

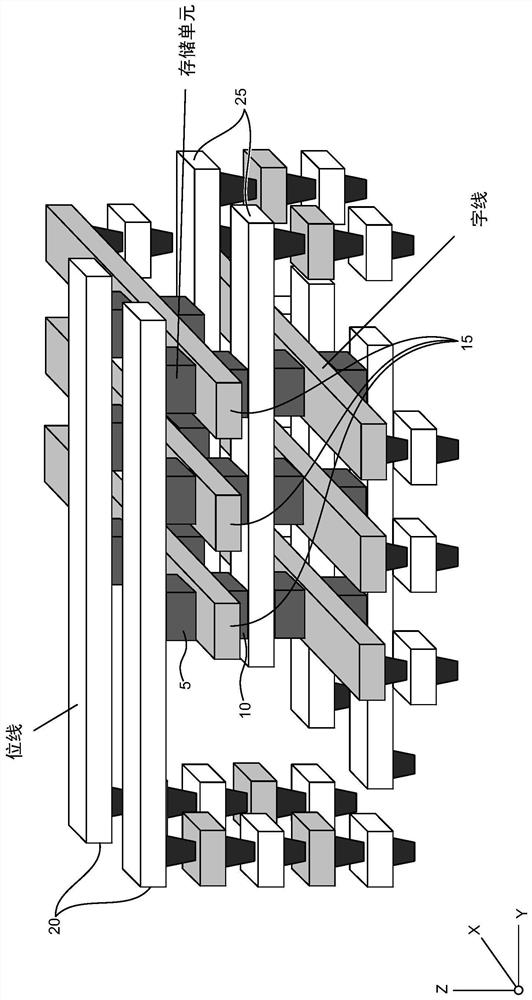

[0037] The presented technique is applied in the field of three-dimensional memory. figure 1 A generalized example of a three-dimensional (3D) memory is shown. in particular, figure 1 is an isometric view of a segment of a 3D intersection memory. The memory includes a first layer storage unit 5 and a second layer storage unit 10 . Between the memory cells of the first level 5 and the memory cells of the second level are a certain number of word lines 15 extending in the horizontal or X direction. Above the first layer of memory cells 5 is a certain number of first bit lines 20 extending in the vertical or Y direction, and below the second layer of memory cells is a certain number of second bit lines 25 extending in the Y direction.

[0038] In addition, if figure 1 As shown in , the sequential structure of bit line, memory cell, word line, memory cell can be repeated along the Z direction to create a stacked configuration. exist figure 1 In an example, the first layer of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com