A VLSI Database and Design Method Based on Memory Pool

A large-scale integrated circuit and memory pool technology, applied in CAD circuit design, electrical digital data processing, program control design, etc., can solve the problem that the overall performance of the application program is greatly affected, user-defined data cannot be carried, and information or accuracy is lost and other issues to achieve the effect of eliminating complex dependencies, facilitating search, and responding quickly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

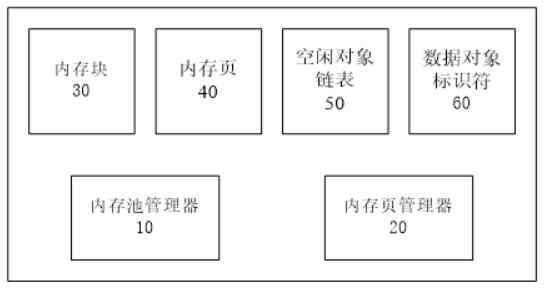

[0053] figure 1 It is a schematic diagram of the VLSI database structure based on the memory pool according to the present invention, such as figure 1 As shown, the memory pool-based VLSI database of the present invention includes a memory pool manager 10, a memory page manager 20, a memory block 30, a memory page 40, a free object list 50, and a data object identifier 60, in,

[0054] The memory pool manager 10 is configured to manage the entire memory pool.

[0055] In the embodiment of the present invention, it consists of a memory pool manager (MemPool), several memory page managers (MemPagePool), several memory chunks (MemChunk) and several memory pages (MemPage). The memory pool manager includes memory pools, which are relatively independent, and different memory pools correspond to different design modules in the chip design. But they are all in the container of the memory pool manager, and correspond to specific chip modules one by one.

[0056] The memory page man...

Embodiment 2

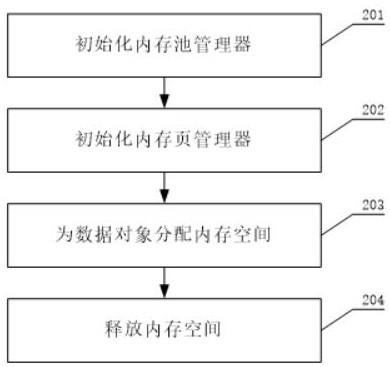

[0067] image 3 For the VLSI database design method flow chart based on the memory pool of the present invention, reference will be made below image 3 , to describe in detail the VLSI database design method based on the memory pool of the present invention.

[0068] First, in step 201, the memory pool manager 10 is initialized.

[0069] In the embodiment of the present invention, the memory pool manager 10 allocates an array space for storing pointers of different memory pools, and at the same time generates a table for mapping the memory pools and circuit design modules.

[0070] In the embodiment of the present invention, after the initialization of the memory pool manager is completed, the program can operate on the circuit design module.

[0071] In the embodiment of the present invention, for a new design module, a new memory pool needs to be allocated for organizing the memory space of the data objects inside it.

[0072] In the embodiment of the present invention, t...

Embodiment 3

[0084] In an embodiment of the present invention, there is also provided an electronic device, including a memory and a processor, wherein a computer program is stored in the memory, and the processor is configured to run the computer program to execute the above memory pool-based The steps of VLSI database design method.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com