Approximate simplification method of single-output combinational logic circuit

A technology of combinational logic circuits and logic circuits, which is applied in the field of approximate calculation of logic circuits, and can solve problems affecting the simplification of logic circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

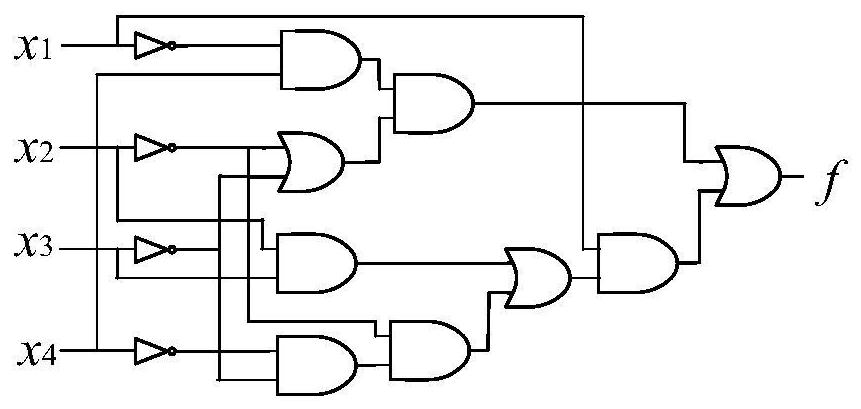

[0075] The first round is calculated as follows:

[0076] Step 1: Assume the single output logistic function is then f(x 1 ,x 2 ,x 3 ,x 4 ) The product term set C composed of all product terms contained in f ={0021,0201,1112,1000}. Assuming an approximation function f a (x 1 ,x 2 ,x 3 ,x 4 ) and the single-output logistic function f(x 1 ,x 2 ,x 3 ,x 4 The number of different minimum items contained in ) cannot be greater than 2, that is, H≤2.

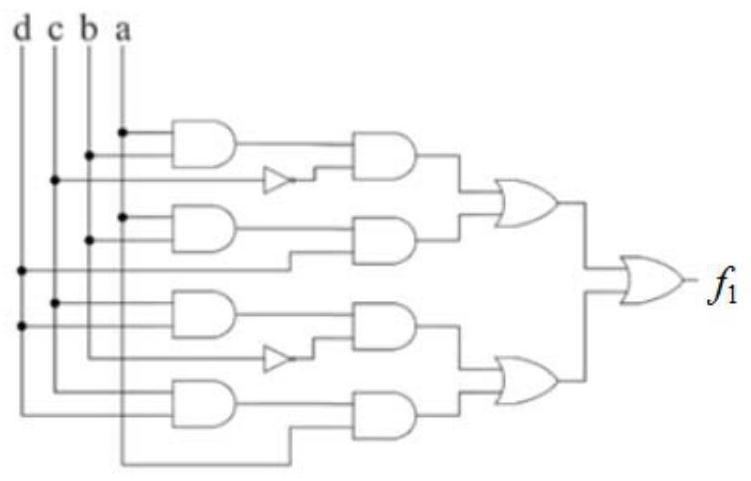

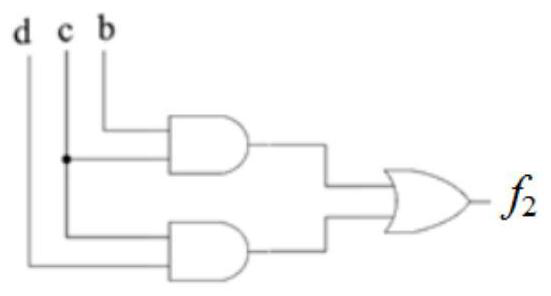

[0077] figure 2 The single output logistic function is given The corresponding circuit diagram, image 3 The single output logistic function is given The corresponding Karnaugh map.

[0078] Step 2: Define the following sets whose initial value is an empty set, denoted as C cur 、C dis 、C dis1 、C RMD 、C tmp 、C er 、C M 、C pnt and C xor .

[0079] Step 3: Choose C f The two product terms in , denoted as p i and p j , assuming p i =(0021),p j =(0201), the product term p i stored in C cur , the product...

Embodiment 2

[0109] Suppose the single-output logistic function is Figure 8 is the Karnaugh map corresponding to f. Utilize the method of the present invention to find two p in f z compliant with step 12 p z1 =(0221) and p z2 =(2112), see for details Figure 9 The Karnaugh map shown. p z1 and p z2 Each generates a C er A set of product terms, all of which are C er = {0111} and is stored to C xor , Figure 9 The square marked "T" in the Karnaugh diagram corresponds to the minimum term (0111), and the final C xor ={0111,0111}. due to C xor The two product terms in are equal, after step 14 to step 15, C xor Both product terms are deleted, so we get due to C M ={1000,0221,2112}, wherein the product term (0221) and (2112) intersect, so there is a logical "exclusive OR" relationship between the two product terms, so f can be expressed as Assuming an approximate function f of f a Satisfying H≤1, the minimum term can be delete, get obviously f a Than the original To ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com