Three dimensional integrated circuit

An integrated circuit, three-dimensional technology, applied in the direction of circuits, electrical components, electrical solid devices, etc., to achieve the effect of increasing signal bandwidth, improving system functionality, and reducing layer separation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

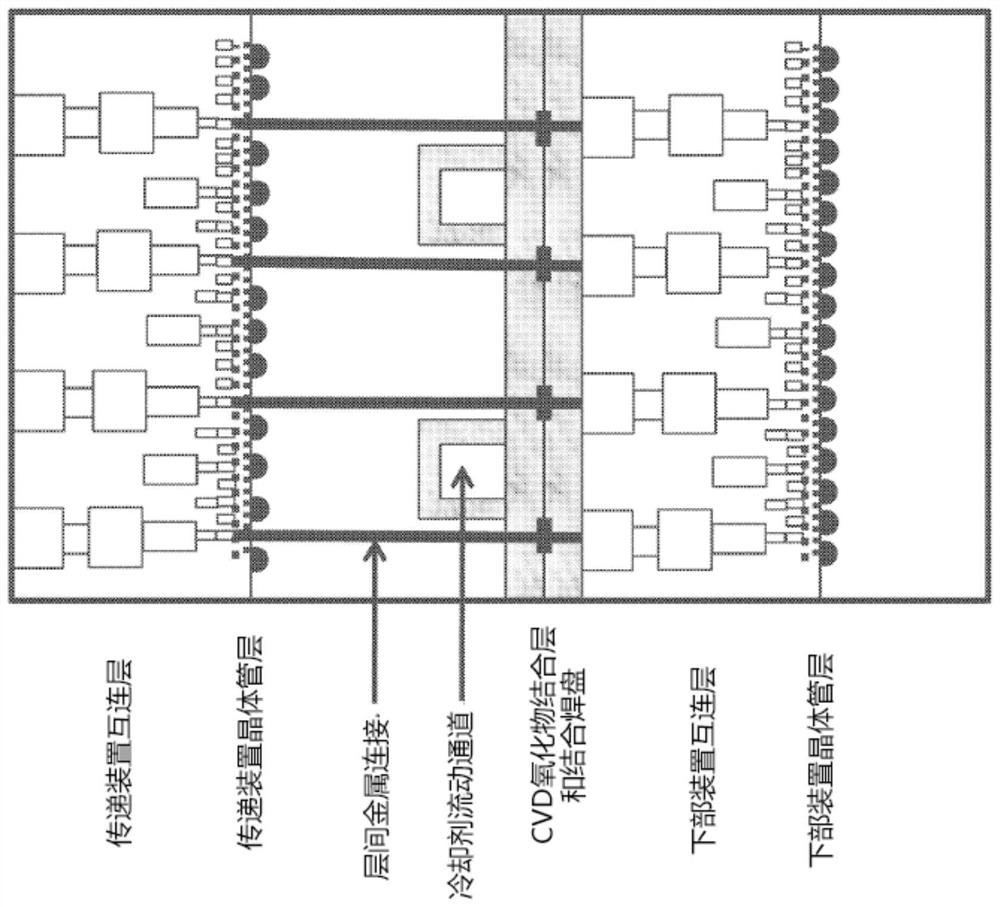

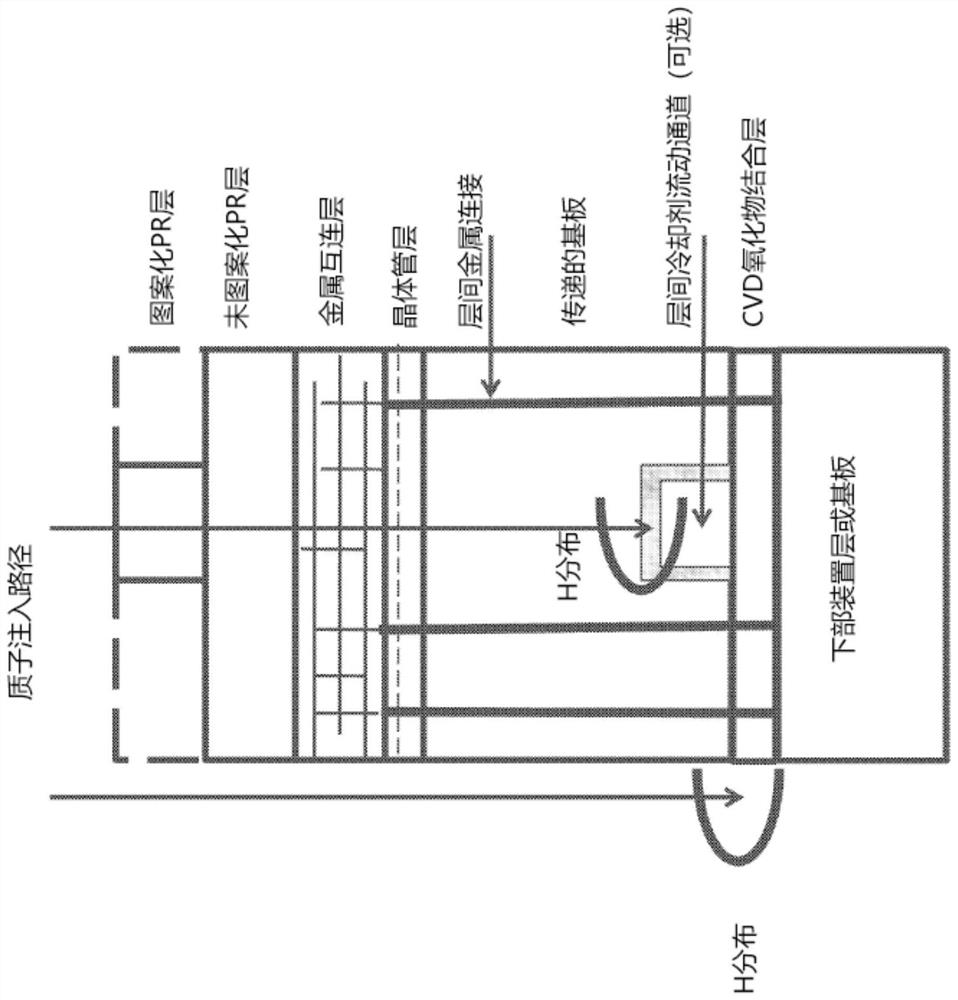

[0086] According to the present invention, techniques generally related to the fabrication of integrated circuit devices are provided. More specifically, the present invention provides a method and resulting devices for stacking and interconnecting three-dimensional (3-D) devices using heterogeneous and non-uniform layers (eg, fully fabricated integrated circuits). For example, an integrated circuit may include, among other things, memory means, processor means, digital signal processing means, application-specific means, controller means, communication means, and the like.

[0087] The embodiments build upon and extend the capabilities of two broad areas of technology, layer transfer methods for forming bonded stacks of homogeneous layers (e.g., forming silicon-on-insulator (SOI) wafers) and various methods currently in use and development, 3-D electronic device stacks are formed through the use of complex interposers and sparse arrays of metal vias for inter-device connectio...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com