Three-dimensional memory and its preparation method

A memory, three-dimensional technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of serious inclination of the upper layer channel holes, affecting the electrical performance of the three-dimensional memory, and the inability to align the lower layer channel holes, etc., to achieve reduction Less risk of tilting, avoiding side wall damage, improving the effect of contour distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

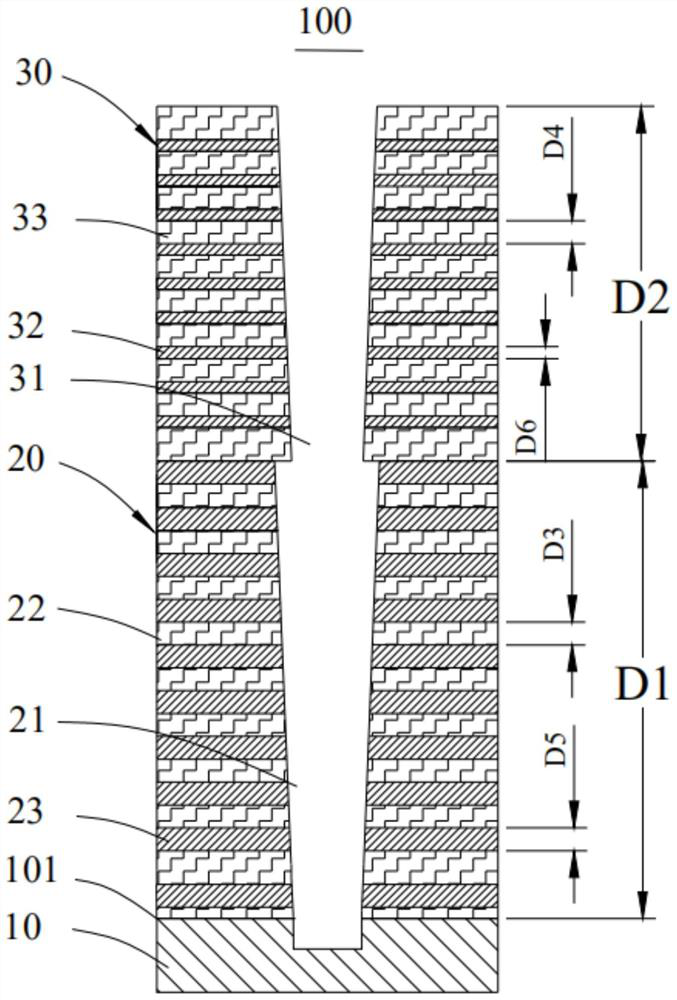

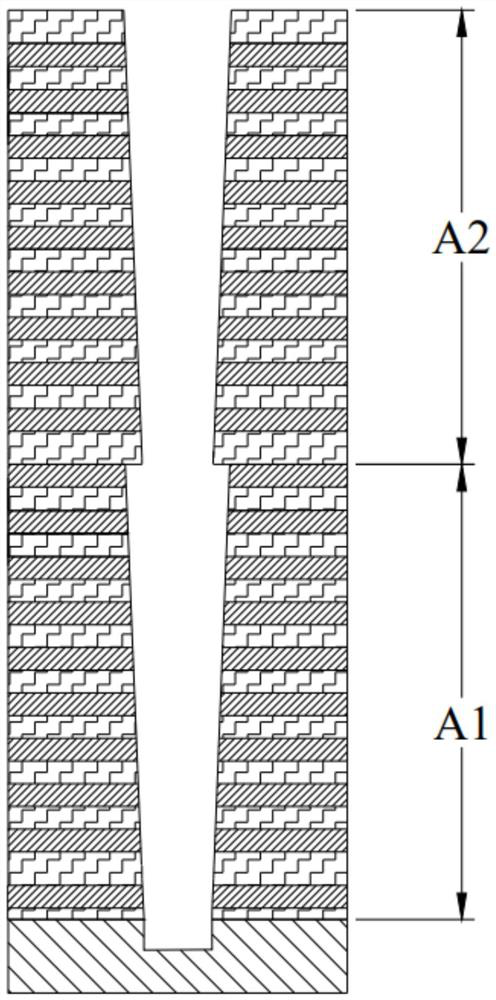

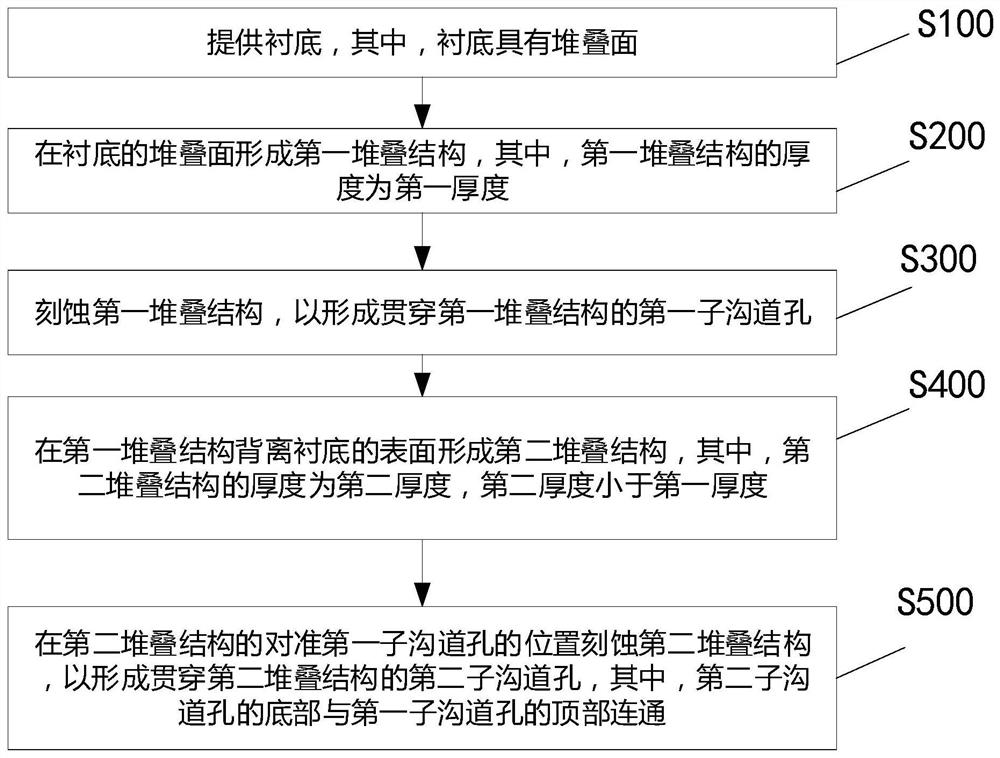

[0039] Specific embodiments of the present invention will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the invention are shown in the drawings, it should be understood that the invention may be practiced in other ways than those described herein, and therefore, the invention is not limited by the following embodiments.

[0040] Three-dimensional (Three dimensional, 3D) stacking technology can form chips or structures with different functions through micromachining techniques such as stacking or hole interconnection to form a 3D three-dimensional memory chip with three-dimensional integration and signal communication in the vertical direction. Three-dimensional (3D) memory uses this technology to three-dimensionally arrange memory cells on a substrate to increase the storage density of the memory.

[0041] Three-dimensional (3D) memory includes 3D NOR (Nor Not) memory and 3D NAND (3D NAND) memory. Compared wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com