Low-power-consumption full adder circuit with reset function

A reset circuit and full adder technology, applied in the field of full adder, can solve the problems of increasing silicon chip area, reducing speed, increasing power consumption, etc., and achieve the effect of overcoming design deficiencies, reducing power consumption, and strengthening control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The technical solutions in the embodiments of the present invention will be described clearly and in detail below with reference to the drawings in the embodiments of the present invention. The described embodiments are only some of the embodiments of the invention.

[0024] The technical scheme that the present invention solves the problems of the technologies described above is:

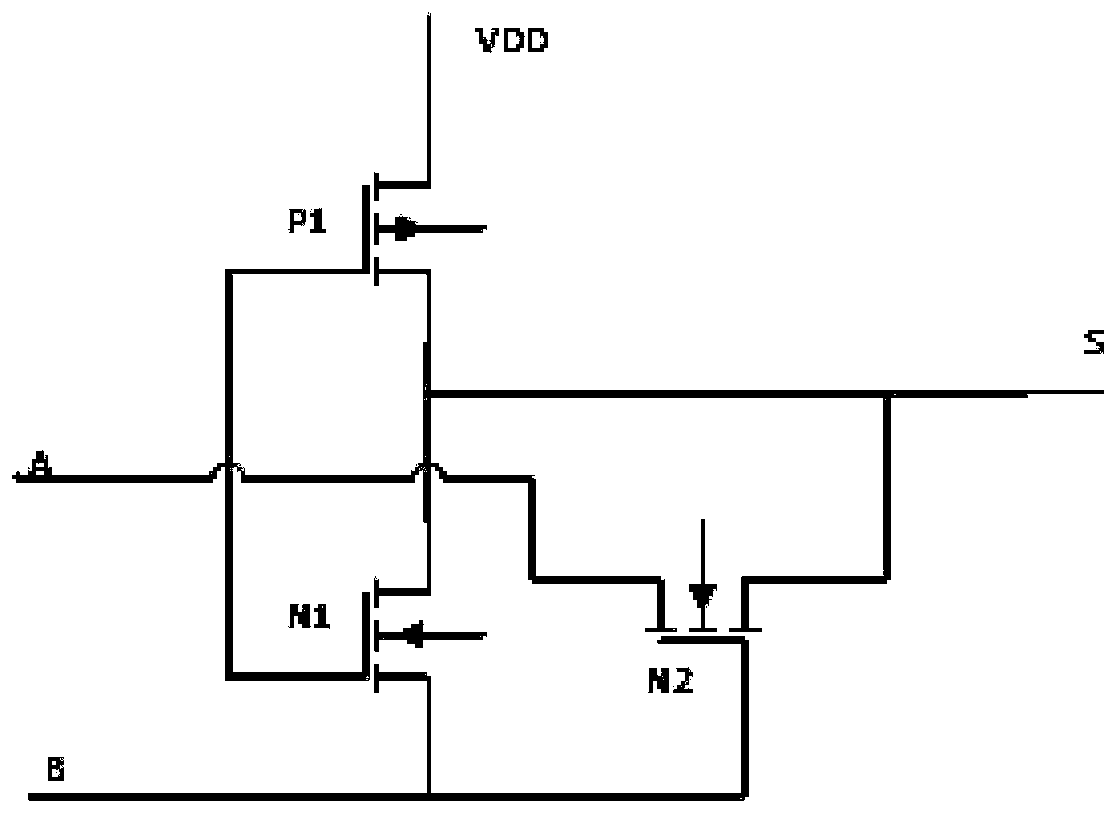

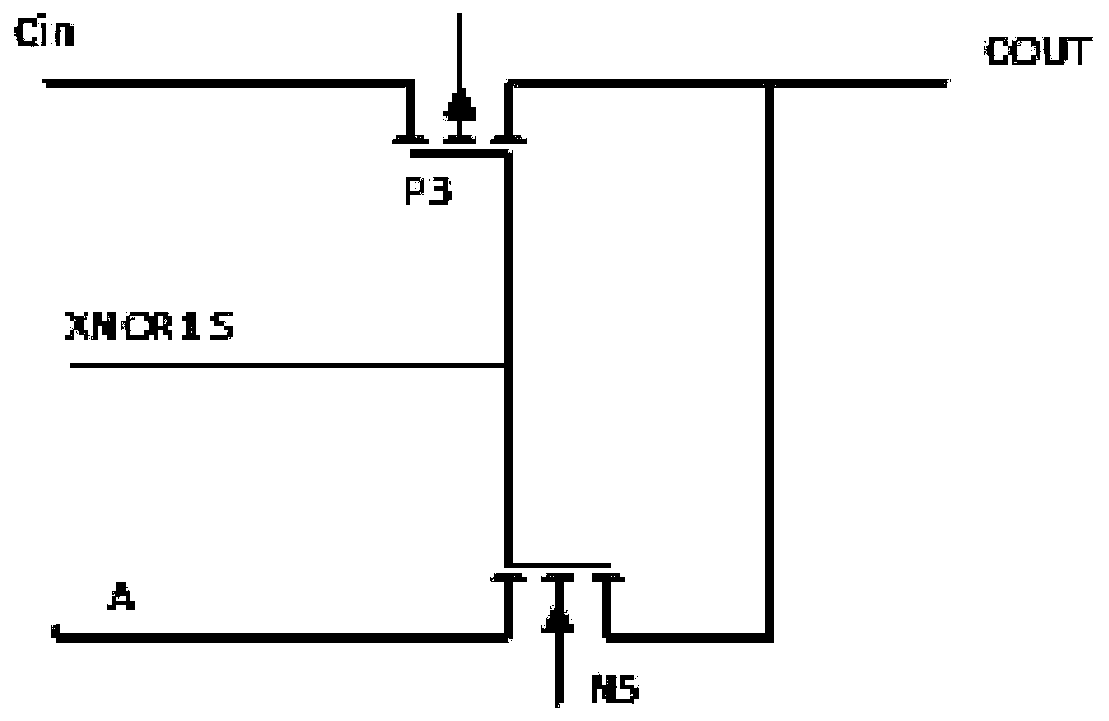

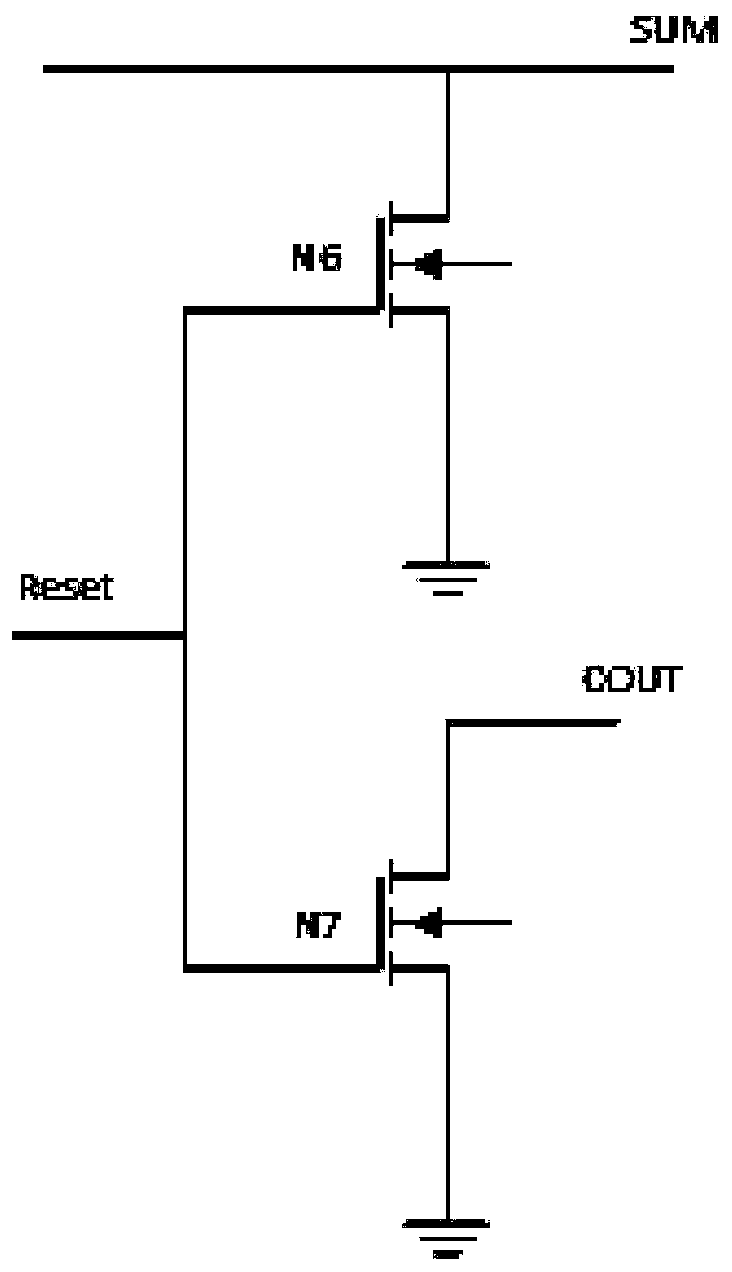

[0025] Such as Figure 5 The shown low-power full adder circuit with reset function uses a one-bit full adder composed of a reset control circuit and a summation signal generation circuit composed of an NOR circuit and a selector carry signal generation circuit, such as image 3 The shown reset circuit includes NMOS transistor N6 and NMOS transistor N7, such as Figure 1 The summing signal generating circuit of the NOR circuit shown includes PMOS transistor P1, PMOS transistor P2, NMOS transistor N1, NMOS transistor N2, NMOS transistor N3, and NOMS transistor N4, such as figure 2 The sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com