Systolic Array Architecture for Sparse Matrix Operations

A systolic array and sparse matrix technology, applied in the field of computer architecture, can solve problems such as waste, idle high-precision data paths, and lower performance of systolic arrays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

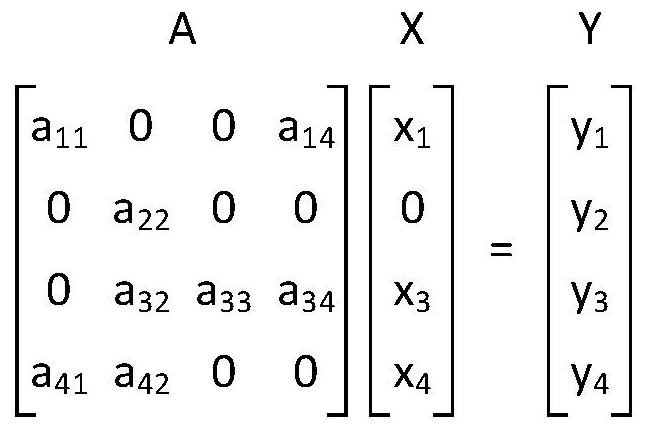

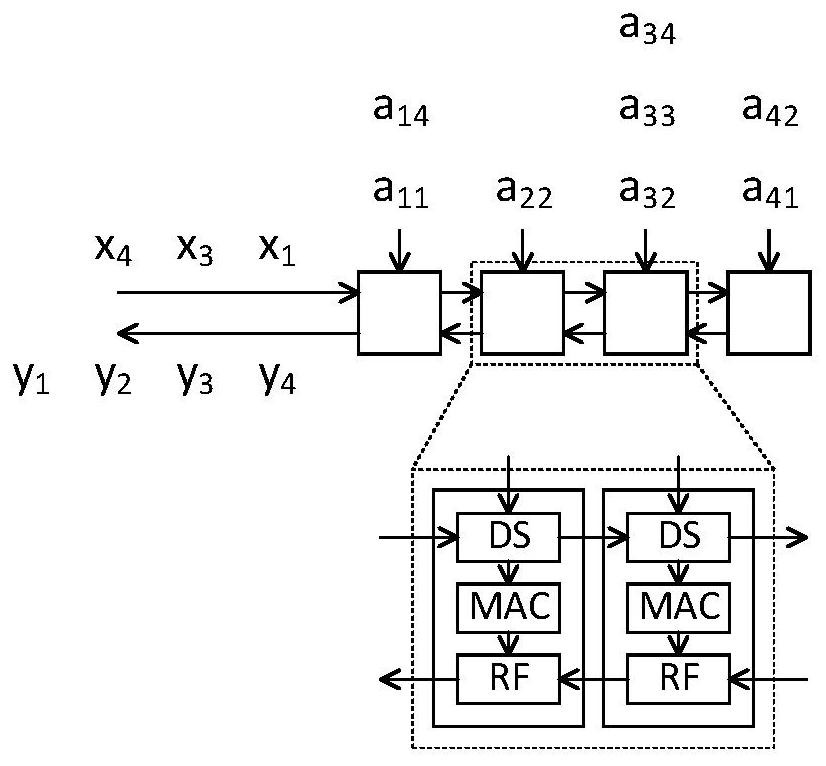

[0052] Aiming at the problem that sparse matrix operations are difficult to be efficiently completed, the present invention proposes a systolic array architecture for sparse matrix operations. While ensuring high parallelism, low memory access bandwidth requirements, and convenient physical design, the architecture removes invalid operations that do not affect calculation results in sparse matrix operations, thereby improving its speed and energy consumption ratio. The present invention is particularly applicable to processing basic general operations such as sparse matrix-vector multiplication, sparse matrix-matrix multiplication, and the like. Next, the present invention will be further described in detail by combining specific embodiments and accompanying drawings.

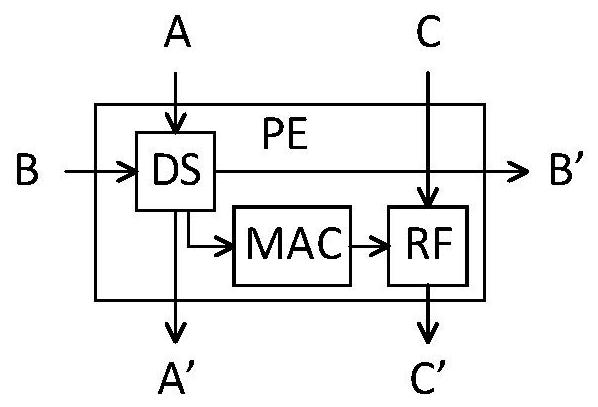

[0053] figure 1 It is a structural schematic diagram of a computing unit (PE) in an embodiment of the present invention. Such as figure 1 As shown, PE consists of three parts: dynamic selection (DS) componen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com