Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems that the electrical performance of the back-illuminated CMOS image sensor cannot be optimized, improved, and cannot be electrically connected, so as to achieve performance optimization, The effect of electrical performance improvement and electrical performance optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] A manufacturing process of a metal grid layer in a pixel area is as follows:

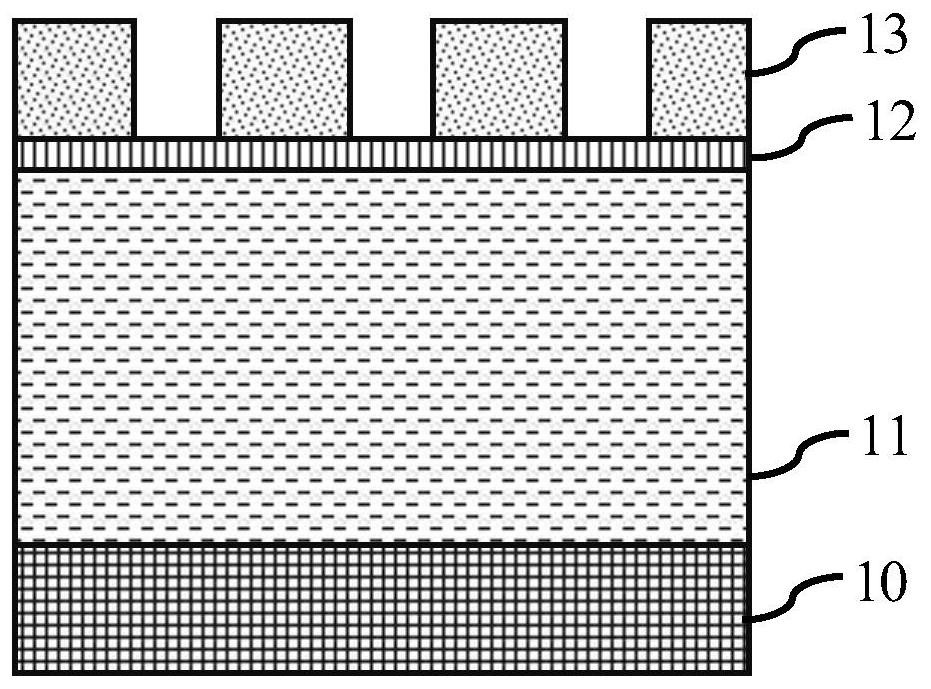

[0061] Such as Figure 1a As shown, a substrate 10 having a pixel region 11 is provided;

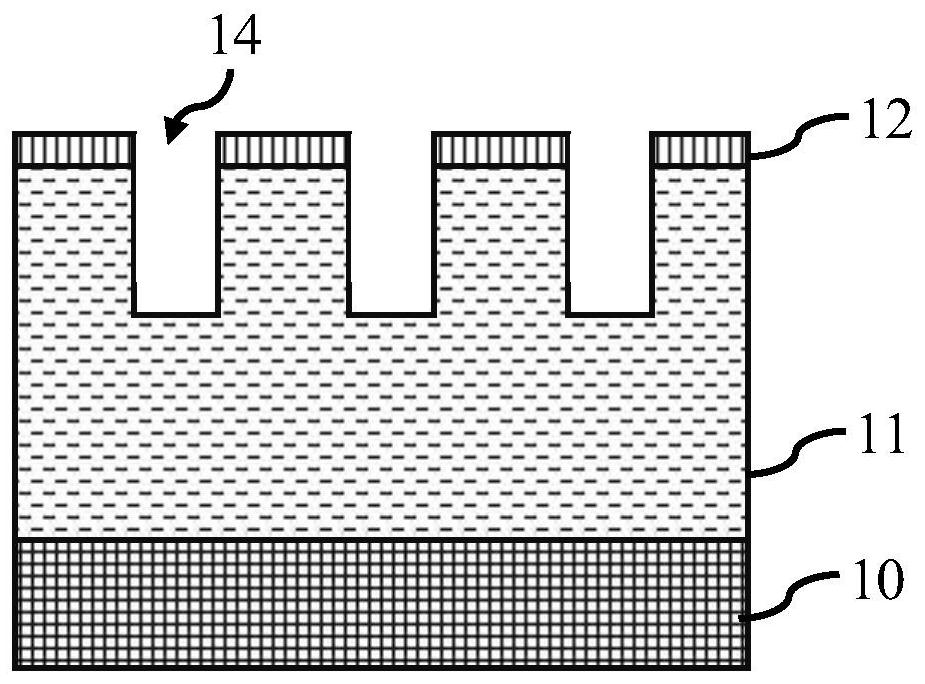

[0062] Such as Figure 1a and 1b As shown, a pad oxide layer 12 is formed on the pixel region 11, a first patterned photoresist layer 13 is formed on the pad oxide layer 12, and the first patterned photoresist layer 13 As a mask, etch the pad oxide layer 12 on the pixel area 11 and the substrate 10 with a partial thickness to form a trench 14 in the substrate 10 of the pixel area 11, and remove the first A patterned photoresist layer 13;

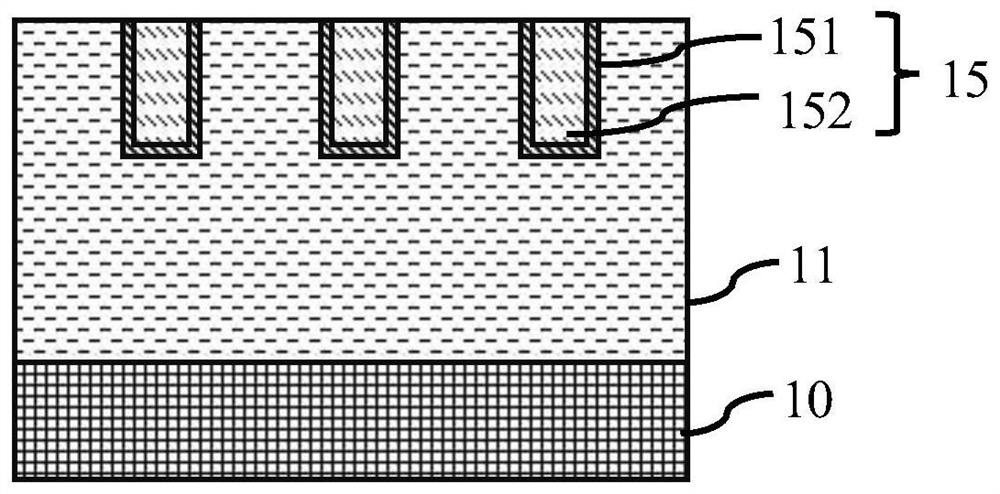

[0063] Such as Figure 1c As shown, an isolation oxide layer 151 is formed on the surface of the trench 14 and the surface of the pad oxide layer 12, and a conductive metal layer 152 is filled in the trench 14, and the conductive metal layer 152 covers the On the pad oxide layer 12, the conductive metal layer 152, the isolation oxide layer 151 and the pad oxide ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com