Low-power-consumption nerve synapse thin film transistor and preparation method thereof

A technology of thin film transistors and neural synapses, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of difficult large-scale integration of organic materials, inability to update weights, difficult large-scale integration, etc., to meet the requirements of Flexible and biocompatible, improve functionality and practicality, and achieve the effect of remembering time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0040] A method for preparing a low-power synapse thin film transistor, including:

[0041] (1) A gate dielectric layer with a thickness of 20-150nm is grown on the upper surface of the back gate electrode by atomic deposition technology. During the preparation process, the temperature is controlled at 30-150°C, and the power of oxygen plasma is 1500-2500 W. The flow rate is 100-180sccm;

[0042] (2) Using physical vapor deposition technology to grow and etch the upper surface of the gate dielectric layer to obtain a conductive channel with a thickness of 30-80nm. During the preparation process, the chamber pressure of the magnetron sputtering is controlled to be 0.5-2Pa, and the temperature is room temperature. The length and width of the channel formed on the upper surface of the source-drain electrode are 5-10 μm and 50-150 μm, respectively;

[0043] (3) Prepare source-drain electrodes by electron beam evaporation;

[0044] (4) performing thermal annealing in a nitrogen a...

Embodiment 1

[0047] An all-inorganic low-power synapse thin film transistor provided in this embodiment has a structure such as figure 1 As shown, the transistor structure from bottom to top is: back gate electrode 1, gate dielectric layer 2, conductive channel 3 and source-drain electrode 4. The source-drain electrode 4 is arranged on the upper surface of the gate dielectric layer 2 , the conductive channel 3 is located on the upper surface and both sides of the source-drain electrode 4 , and a channel is formed on the upper surface of the source-drain electrode 4 .

[0048] The specific preparation process of the transistor is as follows:

[0049] (1) A low-resistance heavily doped p-type silicon substrate is selected for the back gate electrode 1, and the resistivity is <0.005Ω·cm.

[0050] (2) The gate dielectric layer 2 is made of aluminum oxide, using trimethylaluminum (TMA) and oxygen plasma as the precursor and reactant respectively, and grown on the back gate electrode 1 by atomi...

Embodiment 2

[0057] A low-power neural synapse thin film transistor, from bottom to top: a back gate electrode, a gate dielectric layer, a conductive channel, and a source-drain electrode, the source-drain electrode is arranged on the upper surface of the gate dielectric layer, and the conductive channel It is located on the upper surface and both sides of the source-drain electrode, and a channel is formed on the upper surface of the source-drain electrode.

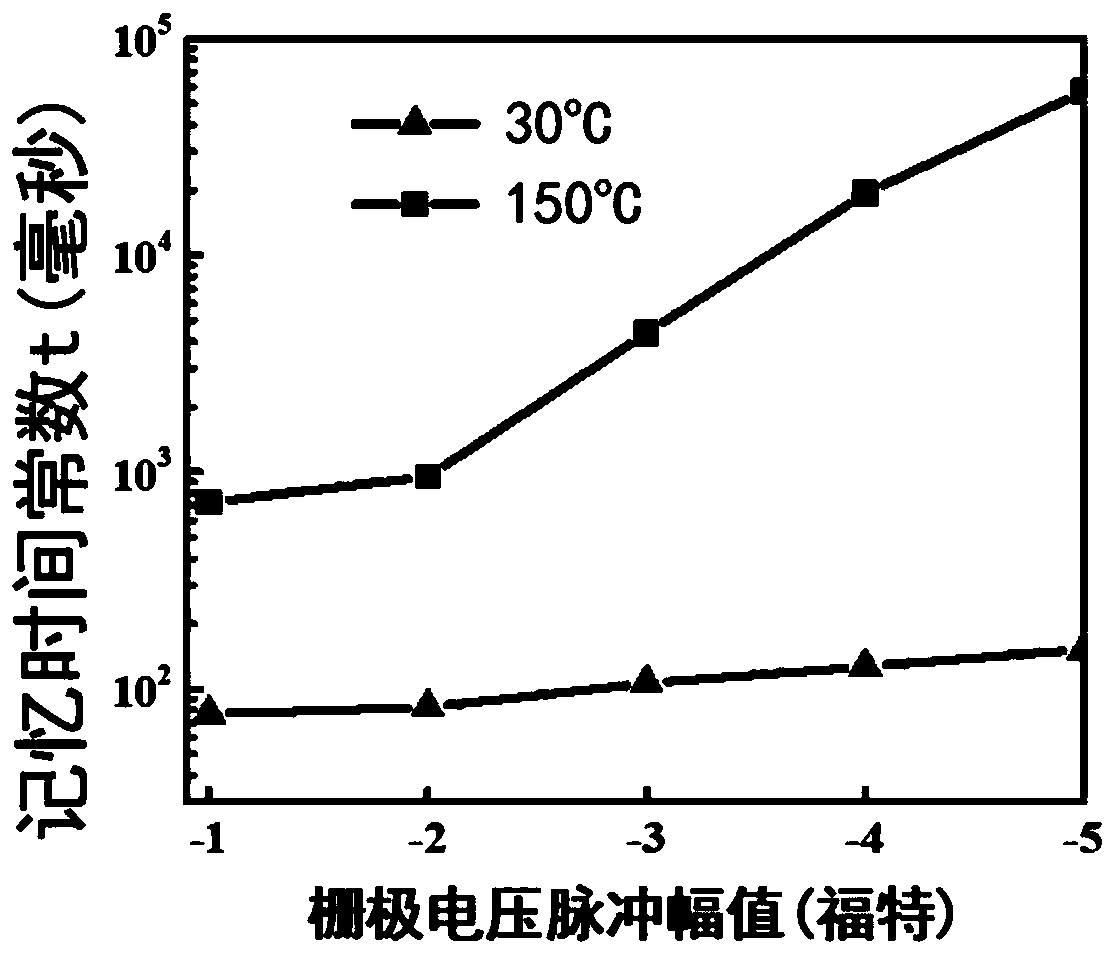

[0058] In this embodiment, the gate dielectric layer is HfO 2 、TiO 2 Composite material, the conductive channel is SnO 2 , the back gate electrode is a low-resistance silicon substrate with a resistivity <0.005Ω·cm. The material selected for the source-drain electrodes is Ti / Au. The synaptic behavior is realized through electron trapping and release through the defects at the interface between the gate dielectric layer and the conductive channel. The defects at the interface between the gate dielectric layer and the conductive ch...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com