Spin storage and calculation integrated chip

A chip and integrated technology, applied in the field of spin storage and calculation integrated chips, can solve the problems of low integration, high static power consumption of massive data, etc., and achieve the effect of improving stability, suitable for large-scale promotion and use, and low storage power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

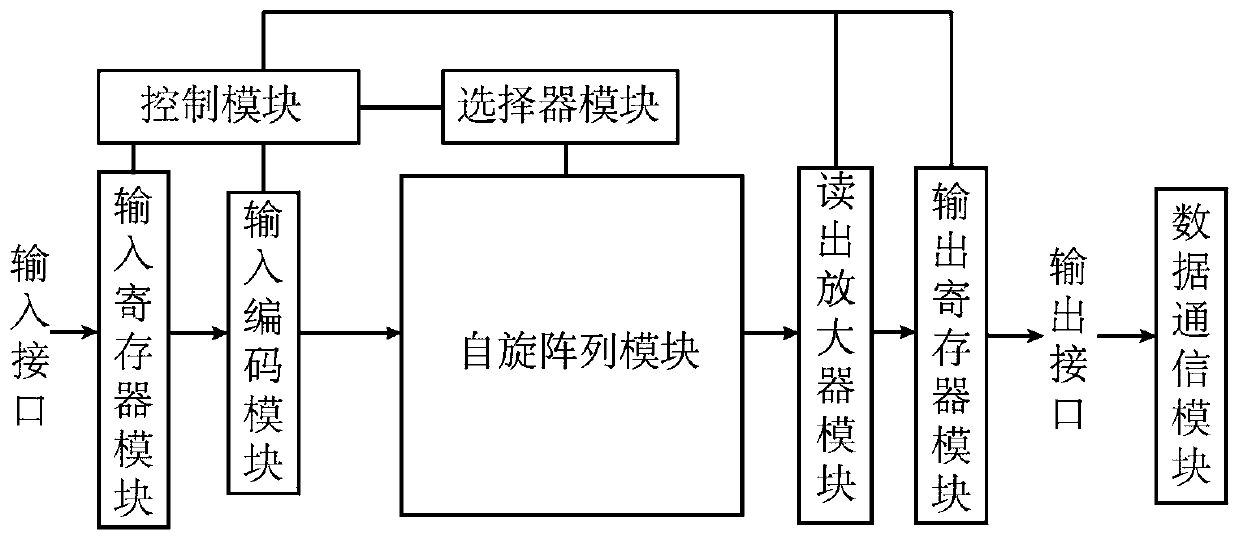

[0071] The embodiment of the present invention discloses a spin-storage-computing integrated chip, such as figure 1 As shown, including: spin array module and peripheral circuits;

[0072] The spin array module is connected with peripheral circuits;

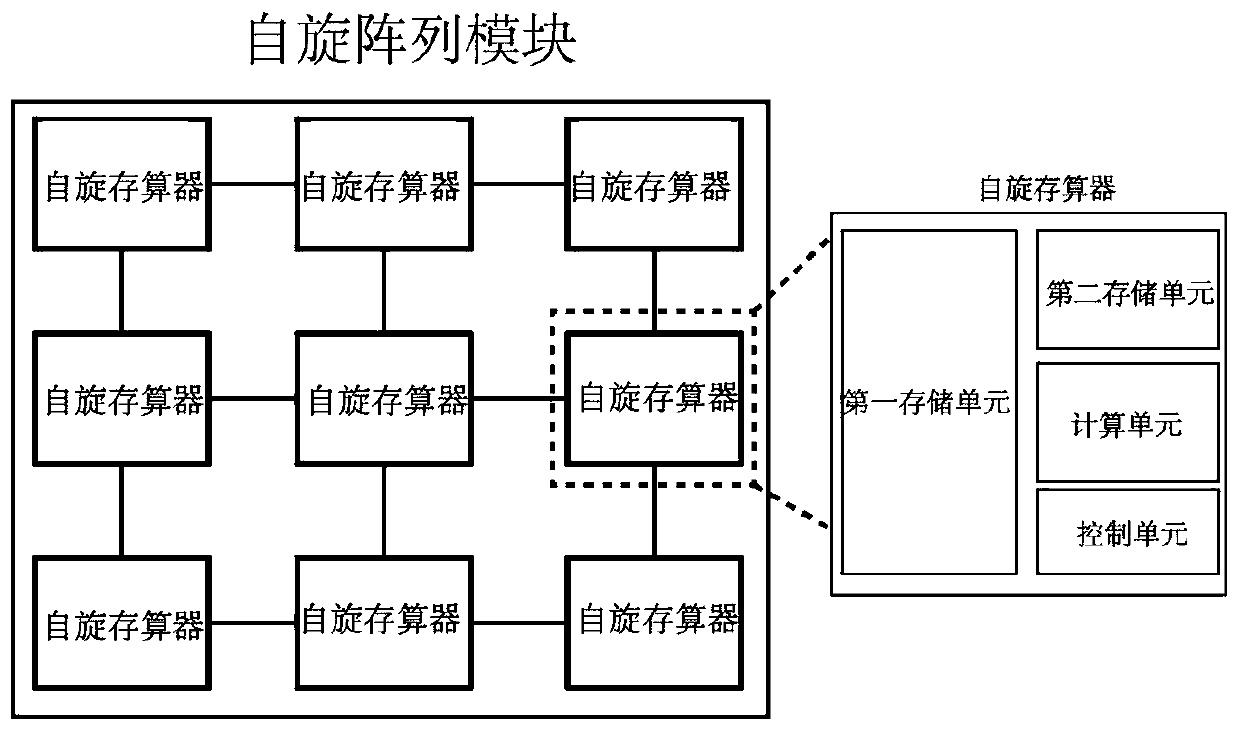

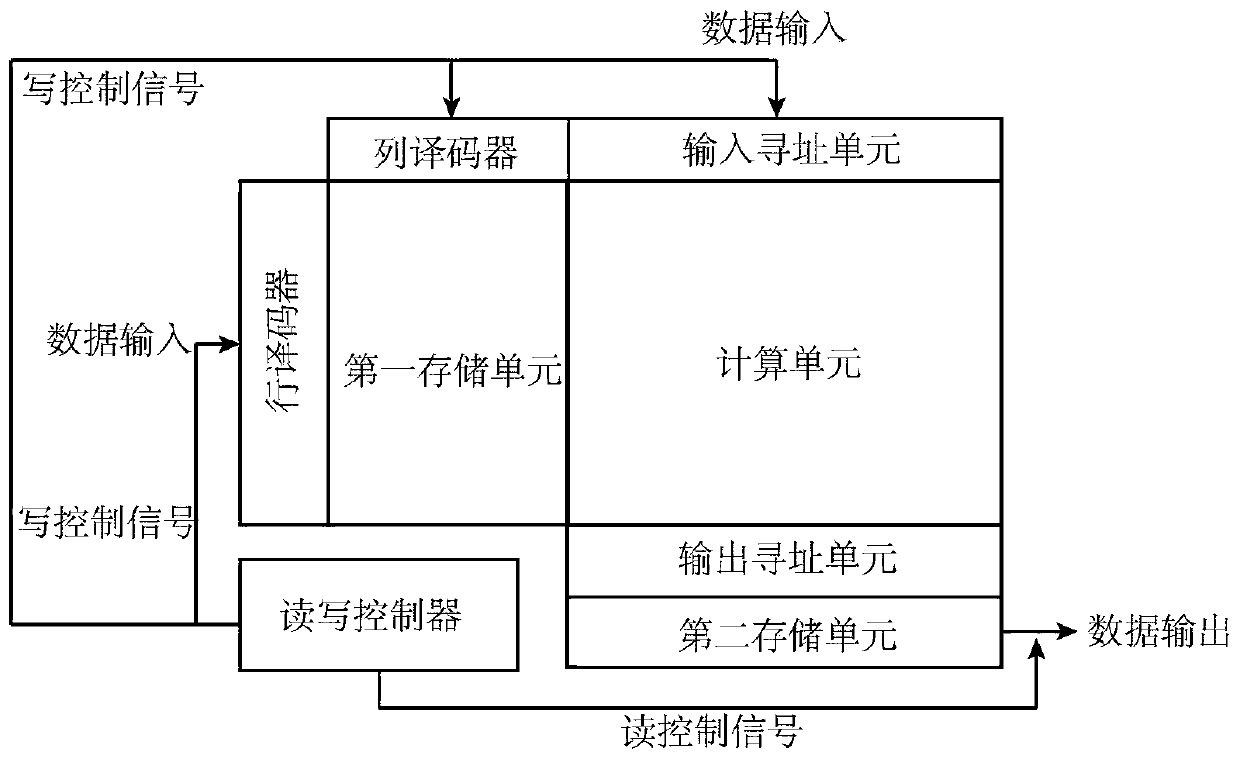

[0073] The spin array module includes more than one spin registers distributed in the array, adjacent spin registers are connected for data transmission, and the spin registers are used for data storage and calculation;

[0074] The peripheral circuit is used to assist the spin register to store and calculate data, including a control module, a selector module, an input register module, an input encoding module, a sense amplifier module, an output register module and a data communication module;

[0075] The control module is used to control the data input and output of the chip and the calculation and storage process;

[0076] The selector module is respectively connected with the spin array module and the control module for s...

Embodiment 2

[0098] An all-in-one chip based on the above spin storage and calculation, such as Figure 8 As shown, a third storage unit may also be included, and the third storage unit is an MRAM storage array, which is used to provide a physically non-copyable function and provide a unique identity for the spin-storage-computing integrated chip.

[0099] It should be further explained that: the third storage unit in this embodiment may exist independently of the first storage unit, or directly use a part of the MRAM storage array in the first storage unit as the third storage unit, which is the same as the first storage unit. A storage unit is connected to the control unit.

[0100]Each chip will inevitably have differences in process parameters during the manufacturing process. The physical non-replicable function is to use the uncontrollable differences introduced by the chip manufacturing process as the characteristic information of the chip. The third storage unit generates a specifi...

Embodiment 3

[0102] A processing terminal including a spin-storage-computing integrated chip includes: a microprocessor and at least one spin-storage-computing integrated chip, and the microprocessor and the spin-storage-computing integrated chip are connected through an interface data line.

[0103] Furthermore, the interface data lines include: serial clock data lines, master device input / slave device output data lines, master device output / slave device input data lines and enable signal data lines;

[0104] The microprocessor transmits the clock signal to the spin-storage-computing integrated chip through the serial clock data line, and the frequency of the clock signal is variable;

[0105] The microprocessor transmits control commands, data to be processed and address signals to the spin memory chip through the master device input / slave device output data line;

[0106] The spin memory chip transmits signals to the microprocessor through the master device output / slave device input dat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com