A method for improving the deposition characteristics of polysilicon thin films for Sonos memory

A polysilicon thin film and memory technology, which is applied in semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of poor polysilicon thin film deposition characteristics, serious wafer warpage, and high temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

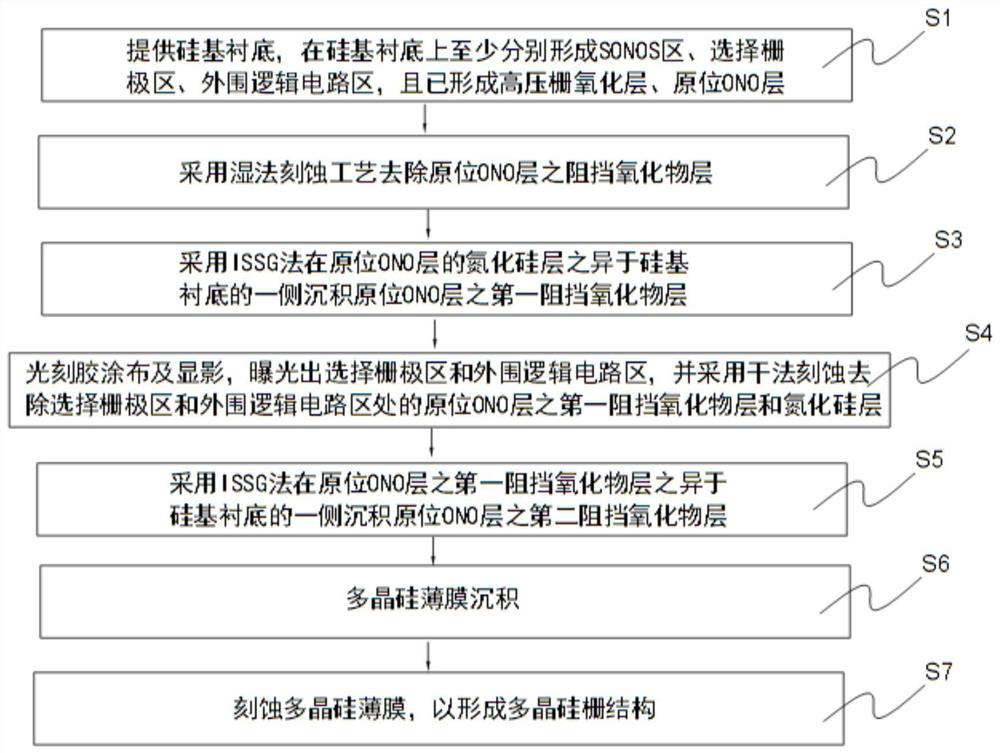

Method used

Image

Examples

Embodiment Construction

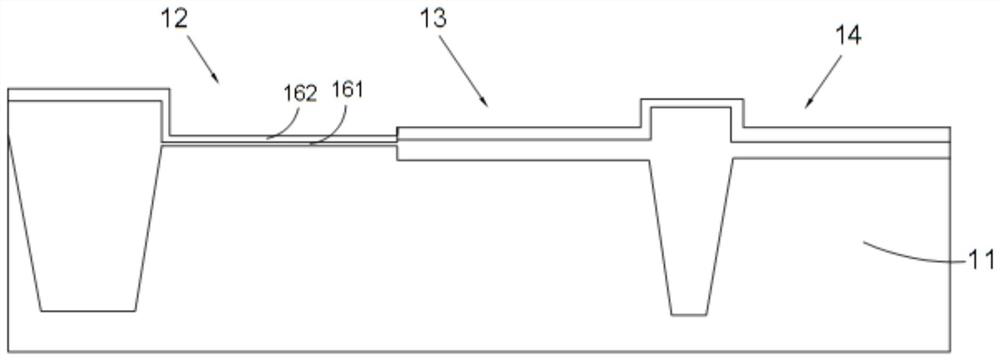

[0025] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

[0026] With the continuous improvement of market requirements for the integration of FLASH storage devices, the contradictions between the reliability of data storage of traditional Flash devices and the working speed, power consumption, and size of devices have become increasingly prominent. SONOS memory has the characteristics of small cell size, low operating voltage, and compatibility with CMOS technology. The continuous improvement of SONOS technology will promote the development of semiconductor memory in the direction of miniaturization, high performance, large capacity, and low cost.

[0027] SONOS memory uses silicon substrate-tunnel oxide layer-silicon nitride-blocking oxide layer (blocking oxide)-polysilicon (Silicon-Oxide-Nitr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com