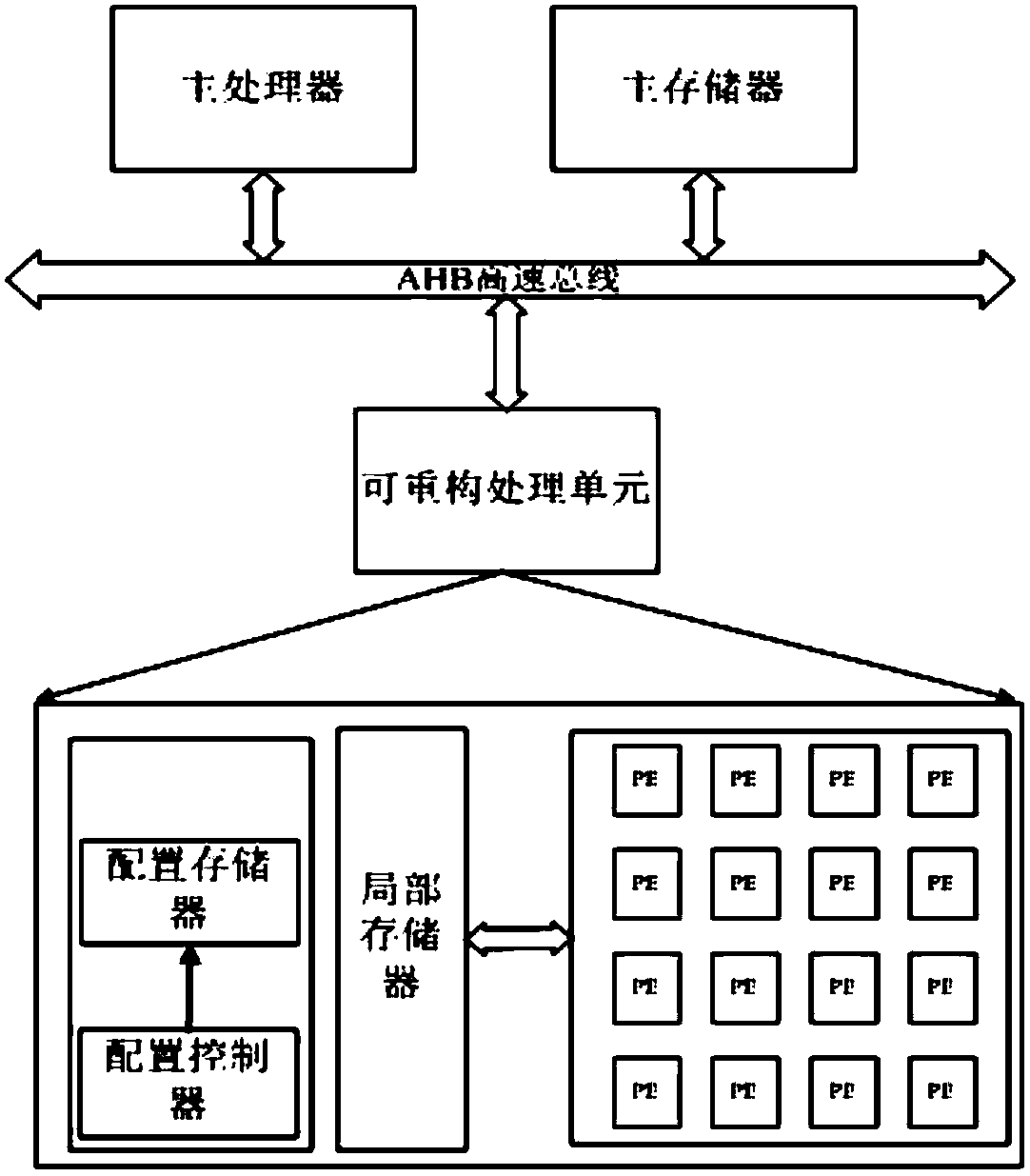

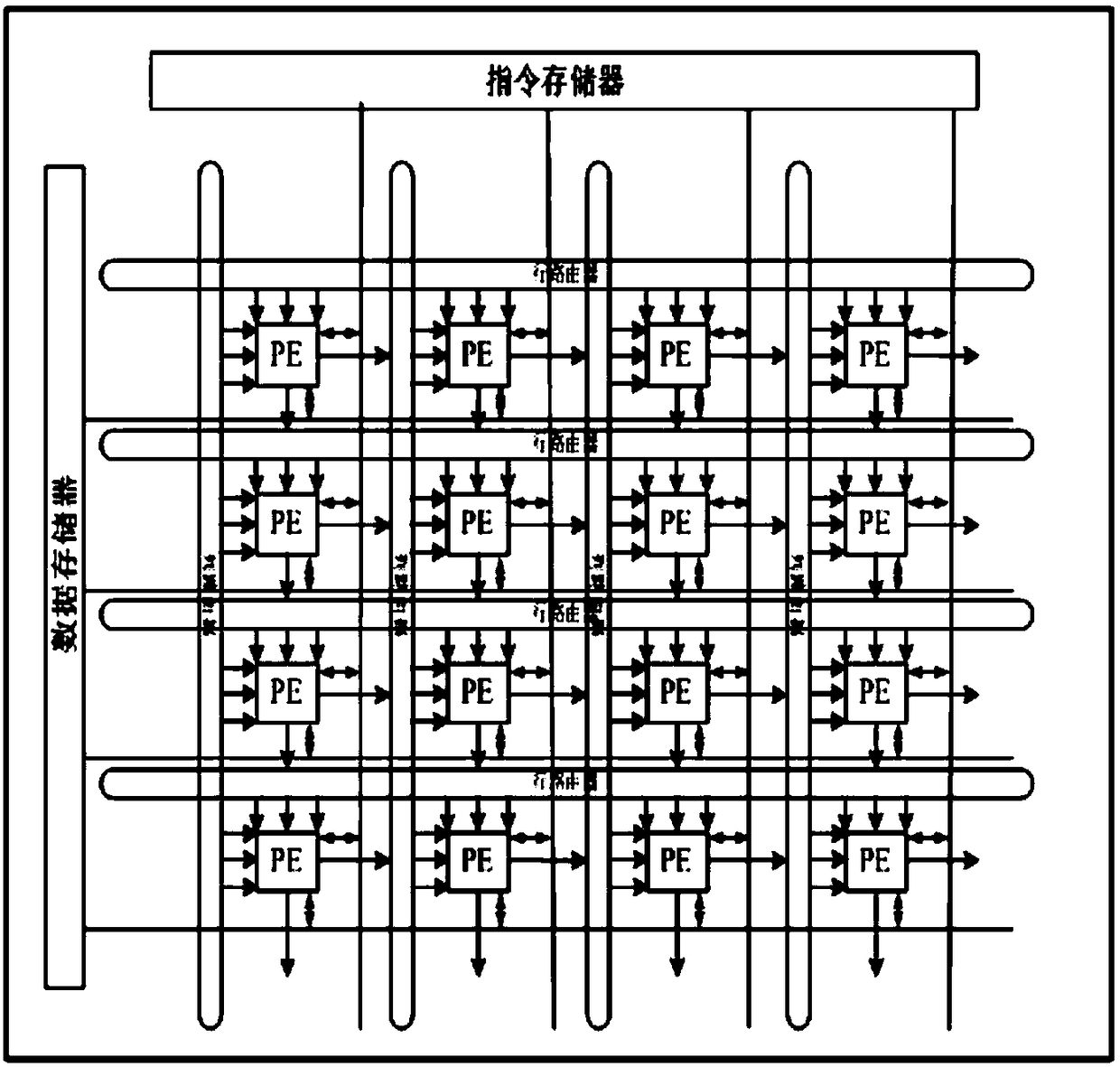

A multi-objective optimization automatic mapping scheduling method for row-column parallel coarse-grained reconfigurable arrays

A multi-objective optimization and automatic mapping technology, applied in multi-programming devices, program startup/switching, program control design, etc., can solve the problems of time-consuming, labor-intensive, complex interconnection constraints of reconfigurable cell arrays, and error-prone.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific example

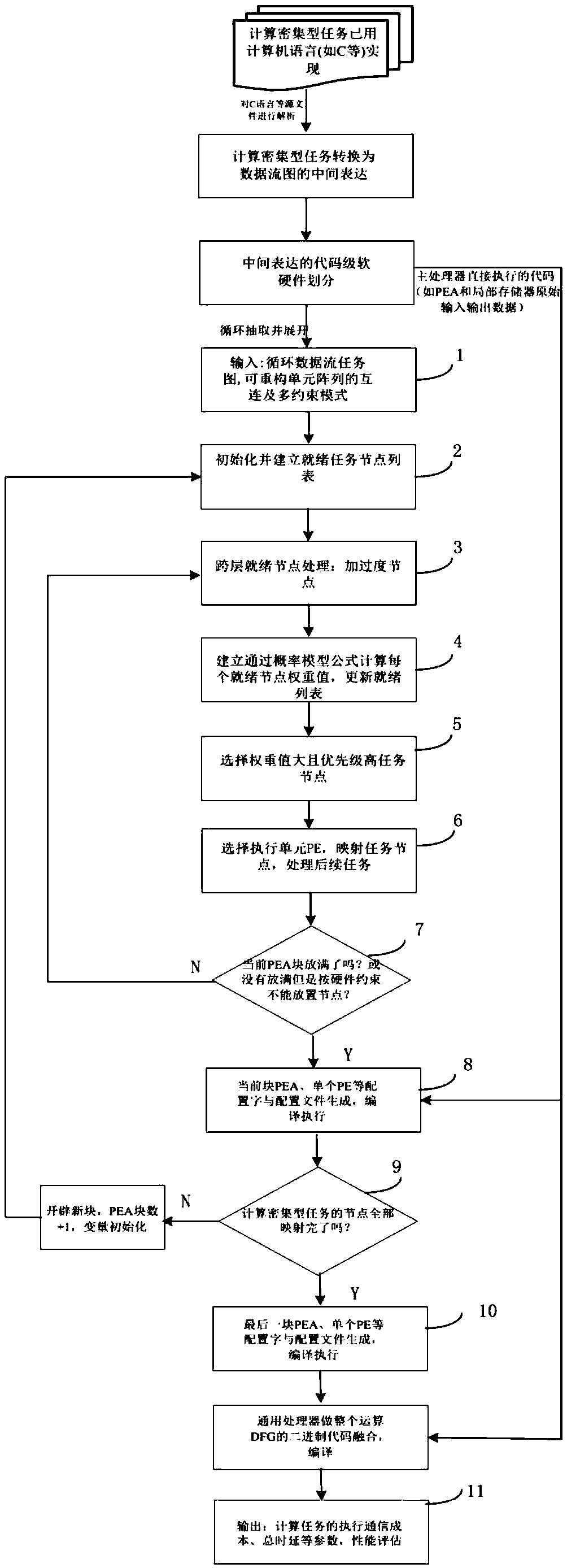

[0051] see image 3 The flow of a multi-objective optimization automatic mapping and scheduling method for row-column parallel coarse-grained reconfigurable arrays, combined with specific examples, specifically includes the following steps:

[0052] Preprocessing step: Computation-intensive tasks have been implemented in high-level languages such as C language, and source files such as C language are parsed and extracted, and converted into intermediate expressions of data flow graph DFG, and code-level software and hardware division of intermediate expressions is performed : The software part of the main processor: the original input and output of the calculation task, which needs to be stored or read through the PEA and the local memory, and the code is directly controlled and executed by the main processor; the hardware array part of the PEA: the key loop for obtaining the calculation-intensive task Intermediate expression of the DFG, which unrolls the cyclic DFG.

[005...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com