Operator mapping method and system for coarse-grained reconfigurable architecture

A technology of architecture and mapping method, applied in the direction of program code conversion, code compilation, etc., can solve the problems of large search space, increased power consumption and area overhead of registers, long compilation time, etc., and achieve good mapping performance, small area and energy Cost-intensive, high-speedup effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062]The present invention will be described in detail below in conjunction with specific embodiments. The following examples will help those skilled in the art to further understand the present invention, but do not limit the present invention in any form. It should be noted that those skilled in the art can make several changes and improvements without departing from the concept of the present invention. These all belong to the protection scope of the present invention.

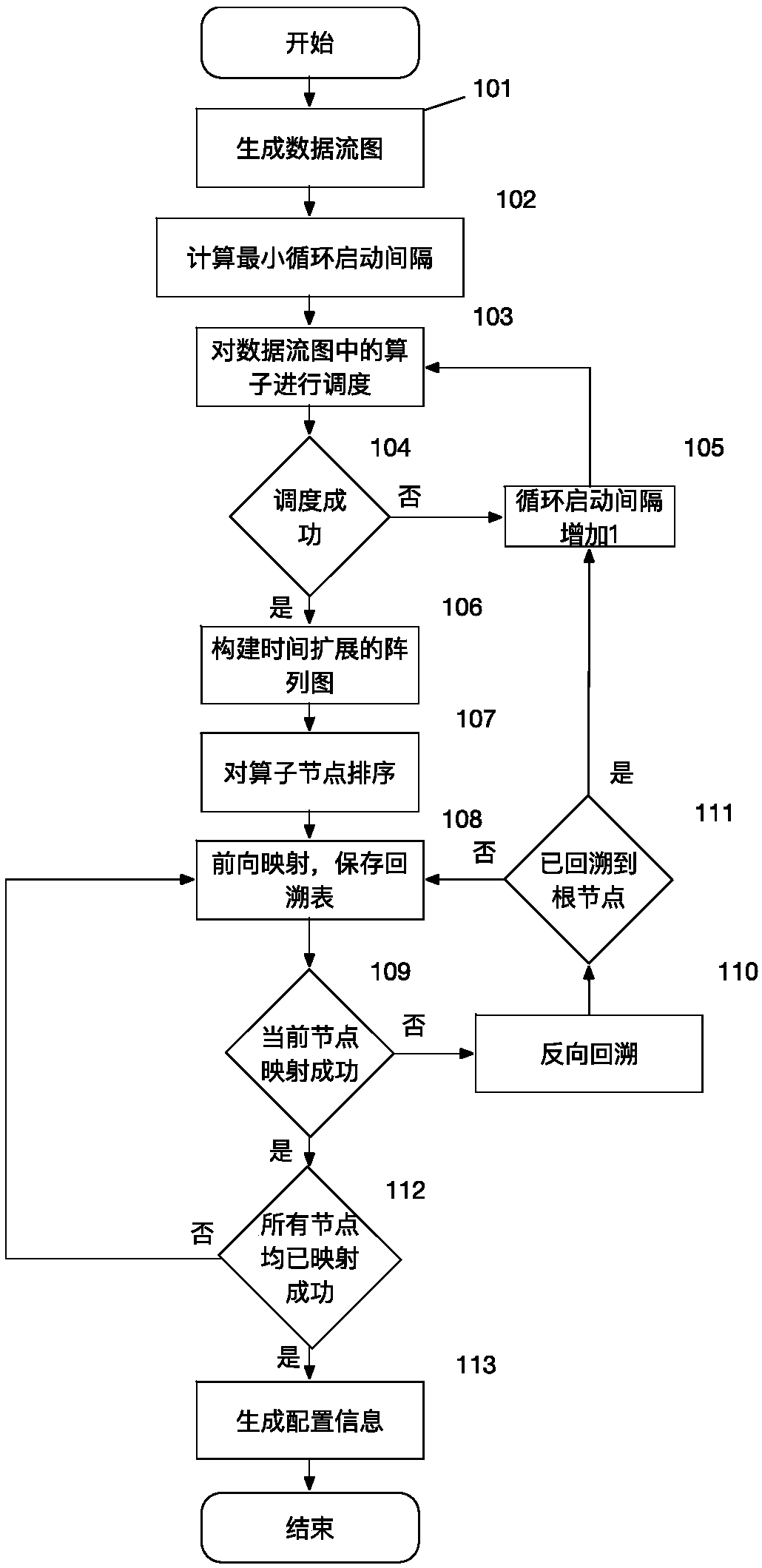

[0063] Such as figure 1 As shown, according to the operator mapping method of a coarse-grained reconfigurable architecture provided by the present invention, it includes:

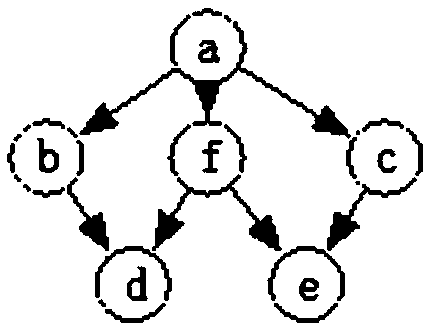

[0064] Data flow graph generation step: generate a corresponding data flow graph (DFG) according to the intermediate language file at the front end of the compiler;

[0065] Calculation step of the minimum cycle start interval: Calculate the minimum cycle start interval according to the number of operators in the data flow graph and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com