A chip with expandable memory

A technology for expanding memory and memory, which is applied in memory address/allocation/relocation, instruments, computers, etc. It can solve the problems of increasing the average hops of memory modules and reducing the speed of memory modules, etc., to achieve load balance, reduce delay, and reduce burden Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention. Obviously, the described embodiments are part of the embodiments of the present invention, not all of them.

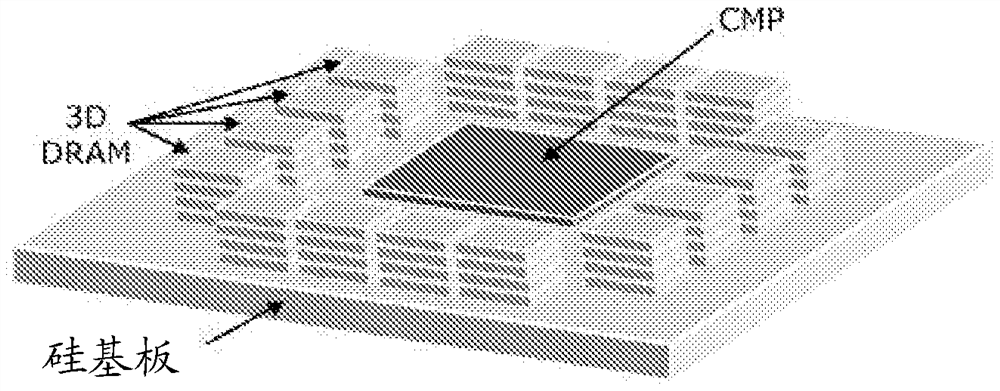

[0031] figure 1 A schematic structural diagram of an expandable memory chip 100 applicable to an embodiment of the present invention is shown. Such as figure 1 As shown, the chip 100 includes a multi-core processor chip (Chip of Multi Processor, CMP), multiple three-dimensional (Three-dimensional, 3D) dynamic random access memory (Dynamic Random Access Memory, DRAM) and the CMP and the multiple A DRAM integrated silicon substrate (silicon interposer), wherein the surface of the silicon substrate can be covered with a metal coating, and the DRAM and CMP can be inverted and integrated on the silicon substrate. A plurality of micro-bumps for communication are arranged bet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com