Method for lowering contact resistance of two-dimensional material field effect transistor

A technology of field effect transistors and two-dimensional materials, which can be applied to circuits, electrical components, semiconductor devices, etc., and can solve problems such as limiting device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] see Figure 1-6 , this embodiment provides a method for reducing the contact resistance of a two-dimensional material field effect transistor, comprising the following steps:

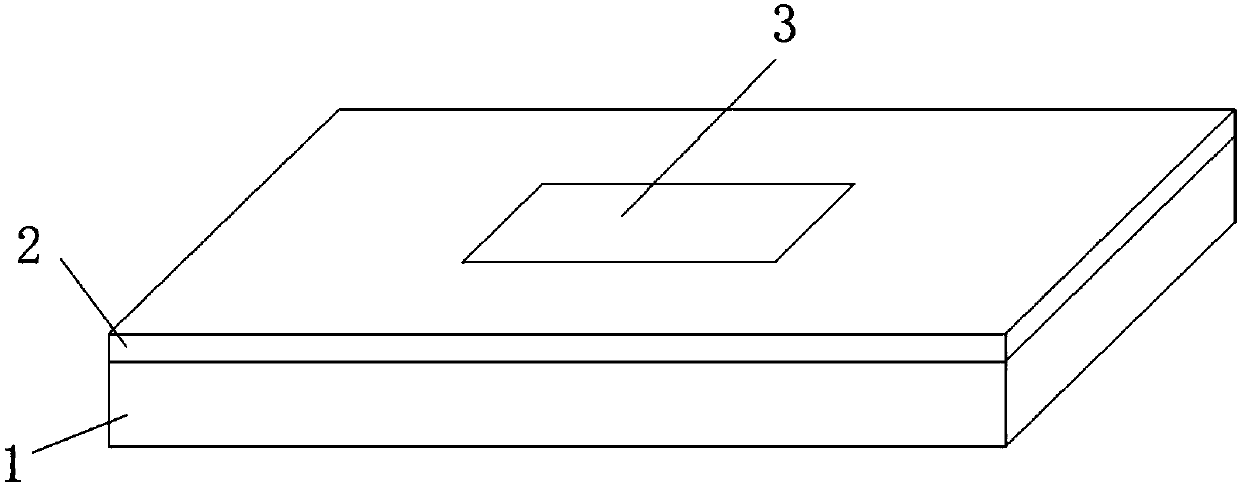

[0055] (1) Prepare the substrate, which is covered with silicon dioxide (SiO 2 ) P-type highly doped silicon wafer, the surface has 100nm thick SiO 2Layer 2 and Si layer 1 at the bottom were cleaned with acetone, ethanol, and deionized water respectively, and then the silicon wafer was blown dry with a nitrogen gun ( figure 1 ).

[0056] (2) Evaporate a rectangular transition metal region 3 on the upper surface of the substrate by electron beam evaporation, magnetron sputtering or atomic layer deposition, the area of which is smaller than the area of the upper surface of the substrate to form a transition metal layer with a thickness of 0.1 nm, the material is Mo( figure 2 ).

[0057] (3) spin-coating photoresist, followed by exposure and development to form a photoresist layer 4, which...

Embodiment 2

[0062] This embodiment provides a method for reducing the contact resistance of a two-dimensional material field effect transistor, including the following steps:

[0063] (1) Prepare the substrate, which is covered with silicon dioxide (SiO 2 ) P-type highly doped silicon wafer, the surface has 200nm thick SiO 2 Layers were cleaned with acetone, ethanol, and deionized water, and then the silicon wafer was blown dry with a nitrogen gun.

[0064] (2) Evaporate a rectangular transition metal region on the upper surface of the substrate by electron beam evaporation, magnetron sputtering or atomic layer deposition, the area of which is smaller than the area of the upper surface of the substrate to form a transition metal layer with a thickness of 0.1nm , the material is Mo.

[0065] (3) Spin-coat photoresist, followed by exposure and development to form a photoresist layer. There are two holes for evaporation source and drain electrodes on the photoresist layer. The holes ar...

Embodiment 3

[0070] This embodiment provides a method for reducing the contact resistance of a two-dimensional material field effect transistor, including the following steps:

[0071] (1) Prepare the substrate, which is covered with silicon dioxide (SiO 2 ) P-type highly doped silicon wafer, the surface has 250nm thick SiO 2 Layers were cleaned with acetone, ethanol, and deionized water, and then the silicon wafer was blown dry with a nitrogen gun.

[0072] (2) Evaporate a rectangular transition metal region on the upper surface of the substrate by electron beam evaporation, magnetron sputtering or atomic layer deposition, the area of which is smaller than the area of the upper surface of the substrate to form a transition metal layer with a thickness of 0.5nm , the material is Pt.

[0073] (3) Spin-coat photoresist, followed by exposure and development to form a photoresist layer. There are two holes for evaporation source and drain electrodes on the photoresist layer. The holes ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com