Element semiconductor lateral super-junction double-diffused transistor with function of optimizing lateral and longitudinal electric fields synchronously

A semiconductor, horizontal and vertical technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of substrate-assisted depletion, limited optimization effect of lateral electric field, uneven distribution of surface electric field, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

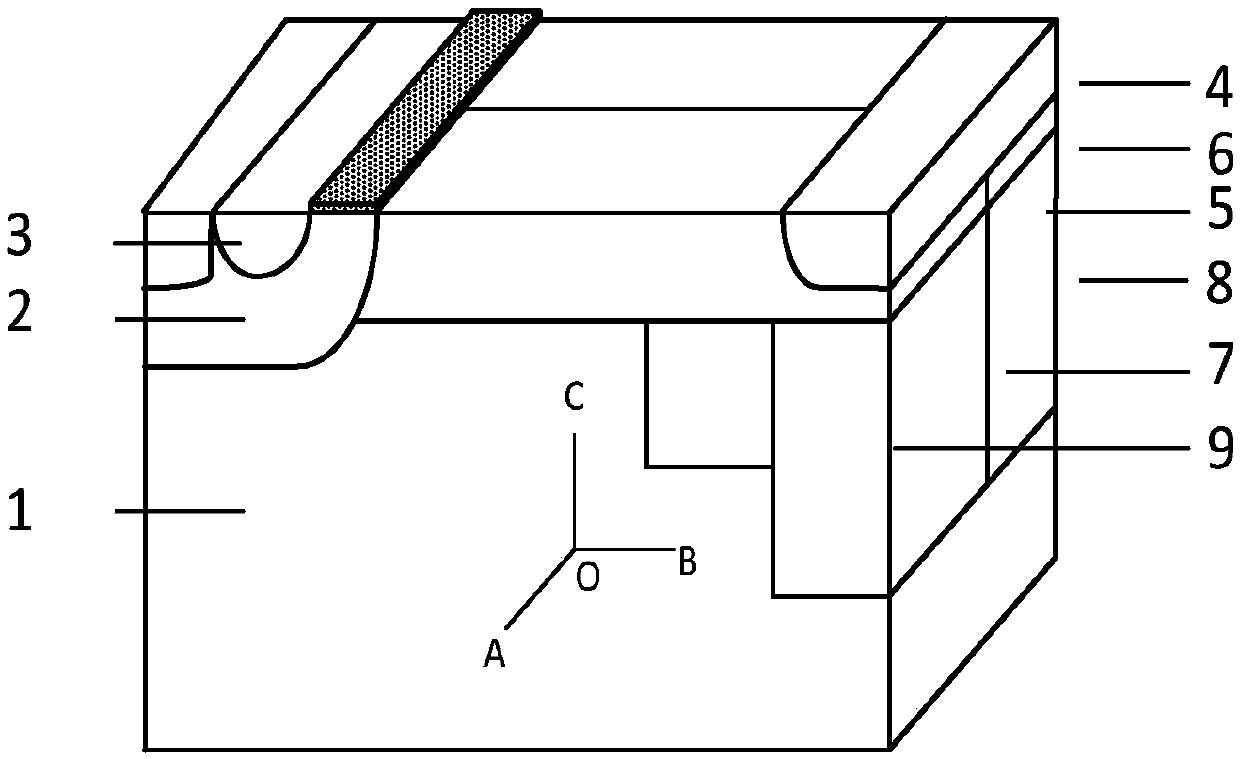

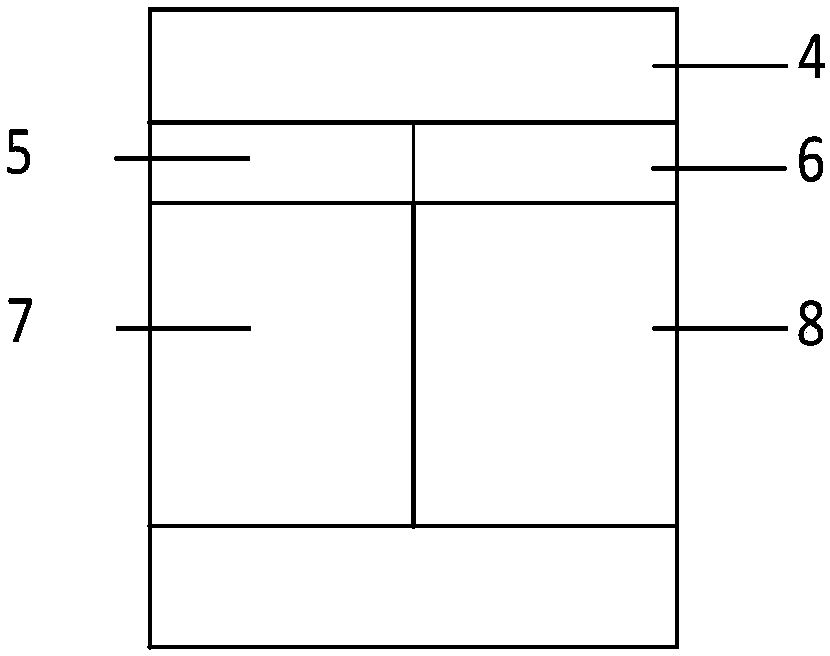

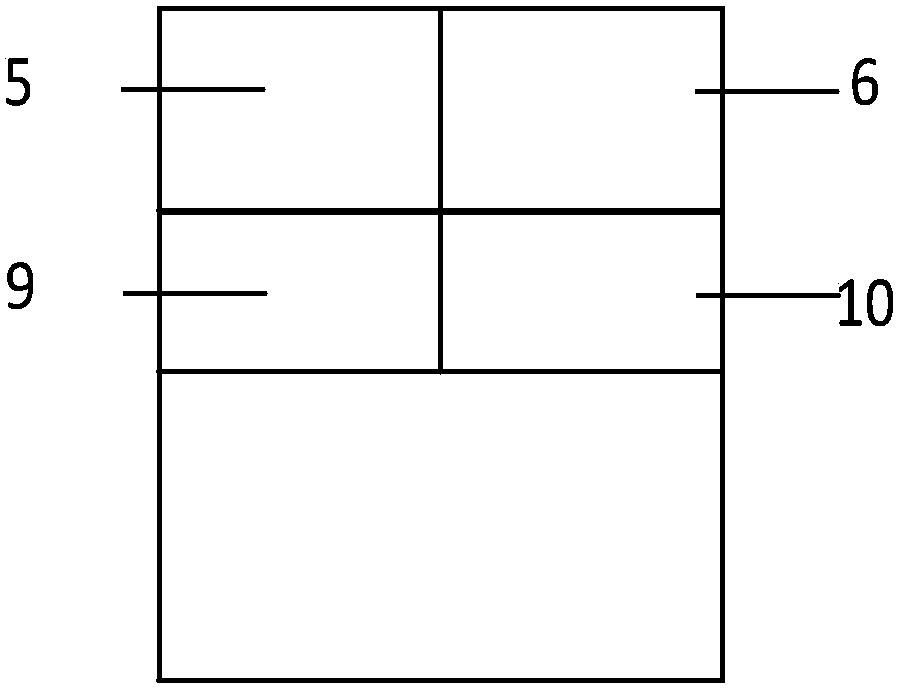

[0040] Such as figure 1 , figure 2 with image 3 Shown is a horizontal superjunction double-diffused transistor with horizontal and vertical electric fields while optimizing the elemental semiconductor:

[0041] Elemental semiconductor material substrate 1, the doping concentration is the concentration of general elemental semiconductor single crystal material, the typical value is 1×10 13 cm -3 ~1×10 15 cm -3 ;

[0042] a base region 2 located on the surface of the elemental semiconductor substrate;

[0043] Implant N columns and P columns on the elemental semiconductor substrate at the edge of the base region, and arrange them alternately to form superjunction (SuperJunction) drift regions 5 and 6;

[0044] a source region 3 located on the surface of the base region;

[0045] The drain region 4 located on the surface of the super junction drift region;

[0046] Below the drift region at the drain end are vertical auxiliary depletion substrate buried layers 7 and 8; ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com