FPGA-based efficient implementation method of Jacobi transformation

An implementation method and high-efficiency technology, applied in the field of efficient implementation of Jacobi transformation, can solve the problems of inability to implement Jacobi signal processing algorithm, multiple hardware resources, and high consumption of FPGA resources, and achieve saving hardware resource consumption, high application value, and calculation speed fast effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

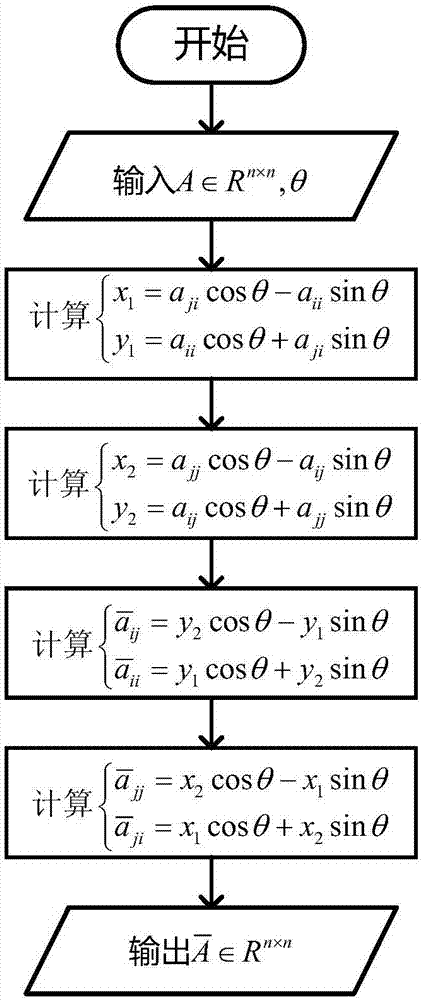

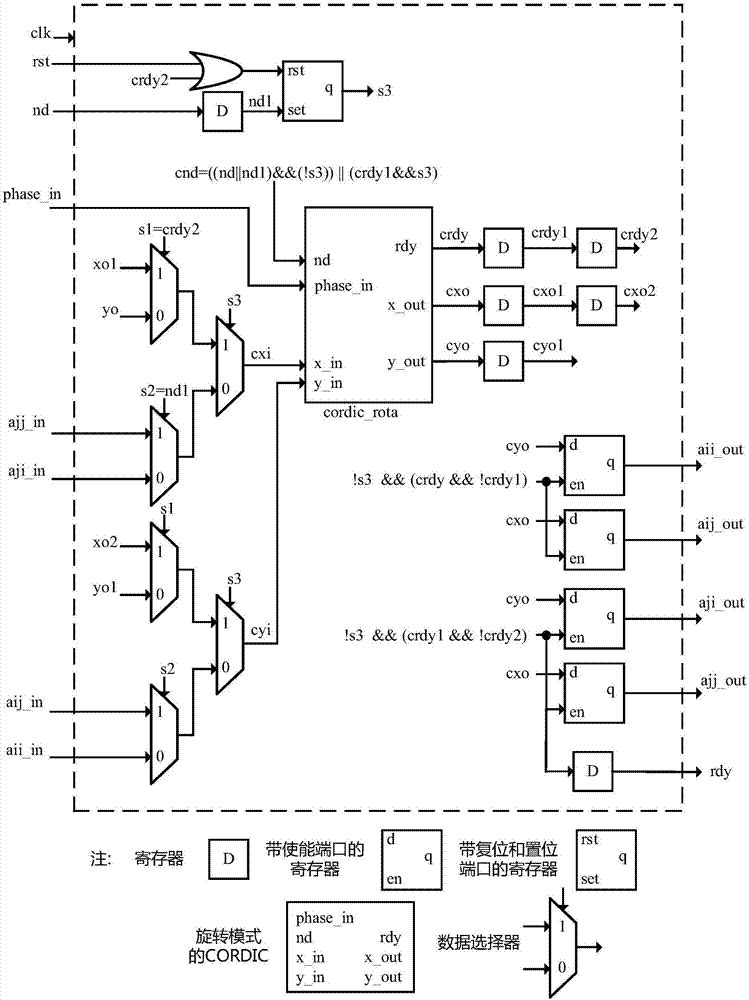

[0033] The algorithm flow of embodiment 1 is as attached figure 2 As shown, the FPGA implementation is attached as image 3 shown.

[0034] Consider a single-baseline phase interferometer, the number of array elements M=2, N=1 carrier is The BPSK-modulated far-field signal s(n) is incident on the single-baseline interferometer at an incident angle of γ=5°, and has an element spacing of d=0.5λ, where λ is the wavelength of the signal. The receiving noise of the array element is Gaussian white noise with zero mean value, and the noise power σ 2 =1, the signal-to-noise ratio of the received signal SNR=15dB, and the number of snapshots L=512. Using L=512 observation samples of the received signal x(n), estimate the eigenvalues corresponding to the signal and the noise.

[0035] The estimated performance of embodiment 1 includes calculation accuracy, calculation speed and resource consumption, specifically evaluated with the following indicators:

[0036] 1. Resource consu...

Embodiment 2

[0068] The traditional solution algorithm is applied to the FPGA implementation of the single-baseline phase interferometer, and the eigenvalues corresponding to the signal and noise are estimated, which is used as a comparative example of Embodiment 1.

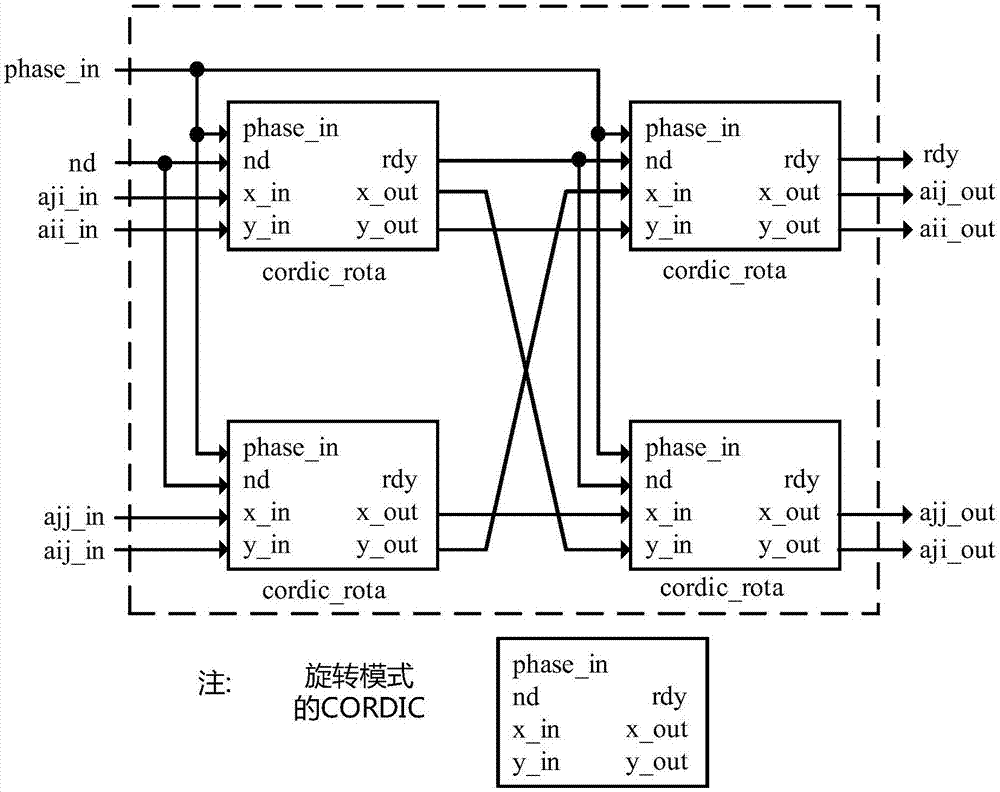

[0069] The FPGA of embodiment 2 realizes as attached figure 1 As shown, the rest of the simulation conditions are the same as those in Embodiment 1, and the eigenvalues corresponding to the signal and noise are estimated.

[0070] The evaluation standard of embodiment 2 is consistent with embodiment 1.

[0071] The simulation result is:

[0072] 1. Resource consumption: N reg =4616,N lut =5024.

[0073] 2. Calculation speed: N clk =46.

[0074] 3. Calculation accuracy: the estimation accuracy of the corresponding eigenvalue of the signal ε 1 =1.8326×10 -5 , the estimation accuracy of the noise corresponding to the eigenvalue ε 2 =1.1378×10 -4 .

[0075] From the above results, it can be seen that the FPGA chip ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com