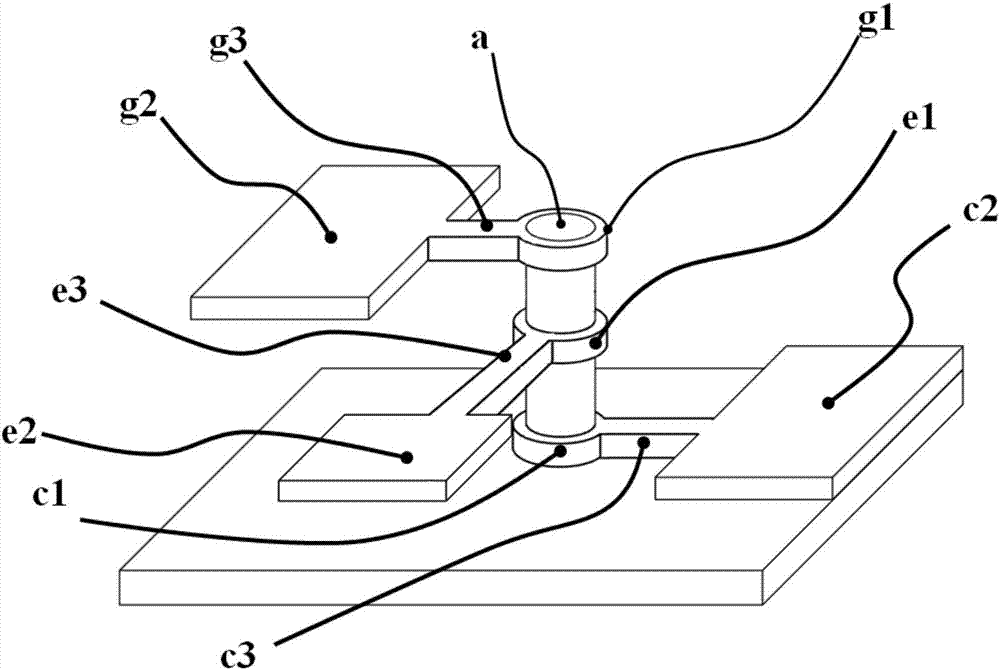

Vertical channel heterostructure metal-insulator-semiconductor field-effect transistor (MESFET) device and fabrication method thereof

A vertical channel and channel technology, which is used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing process complexity, high voltage and high temperature resistance, and unsatisfactory radiation resistance. Achieve the effect of increasing the operating frequency of the device, simplifying the process difficulty, and improving the yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

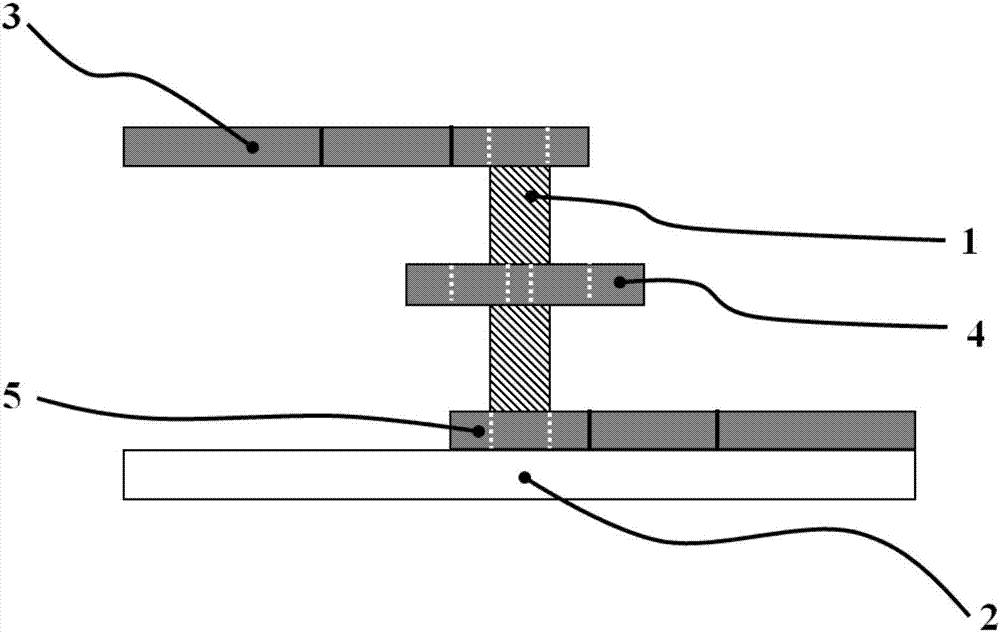

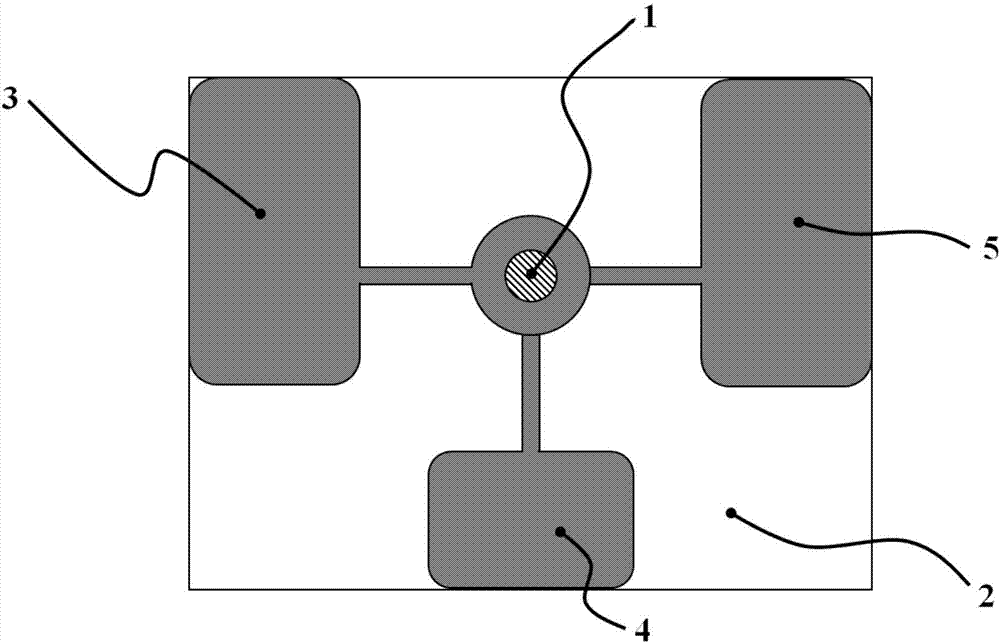

[0065] Further, the preparation method may further include: forming a channel array formed by a plurality of semiconductor channels on the main plane of the substrate, and then fabricating the source, gate and drain.

[0066] Further, the preparation method further includes: forming a Schottky contact between the gate and the semiconductor channel.

[0067] Further, the preparation method further includes: forming an ohmic contact between the source electrode and the drain electrode and the semiconductor channel.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com