Semiconductor structure forming method

A technology of semiconductor and pseudo-gate structure, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve problems such as increasing the difficulty of manufacturing high-K metal gate transistors, shrinking, and performance degradation of high-K metal gate transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

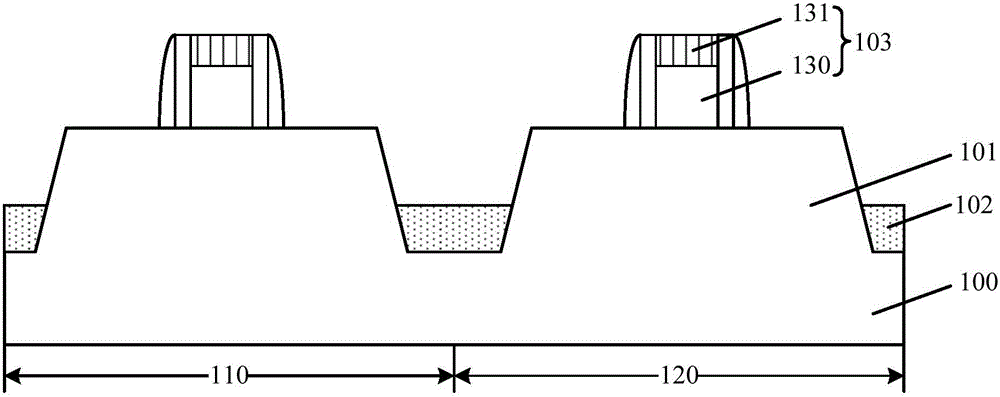

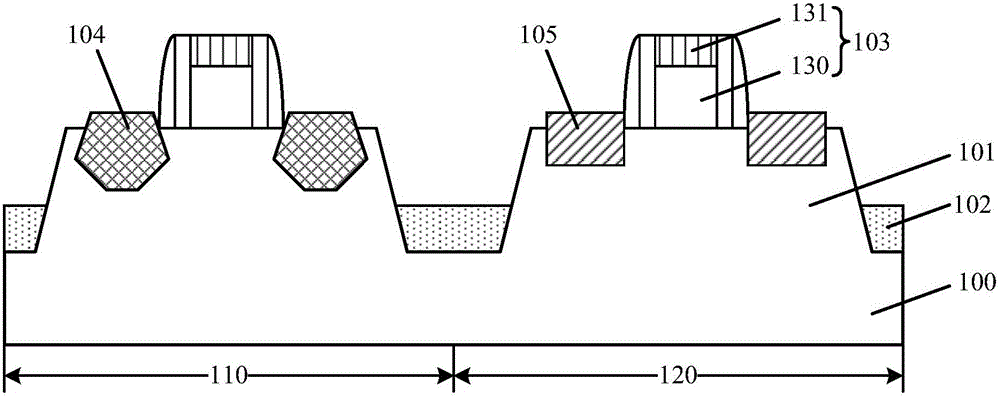

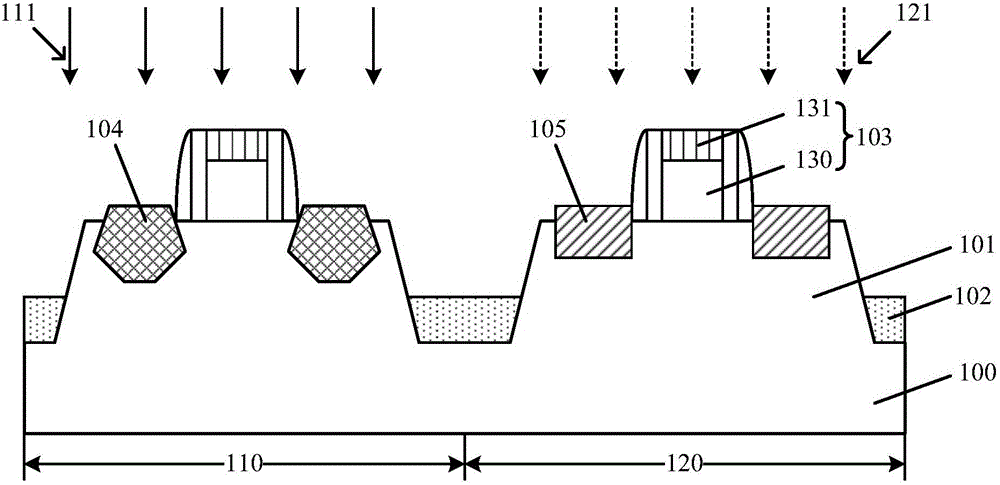

[0032] As described in the background, as the size of semiconductor devices shrinks, the size of the high-K metal-gate transistor is also reduced accordingly, which increases the difficulty of manufacturing the high-K metal-gate transistor, resulting in a decrease in the performance of the high-K metal-gate transistor.

[0033] After research, it is found that since the high-K metal gate transistor is formed by the Gate Last process, however, as the size of semiconductor devices shrinks and the device density increases, in the process of the Gate Last process, the gap between adjacent dummy gate structures The aspect ratio of the trench between them increases, which increases the difficulty of filling the dielectric layer, and the density of the formed dielectric layer is poor, which not only affects the insulation performance of the formed dielectric layer, but also causes the formation of adjacent gates. The parasitic capacitance between pole structures increases, resulting i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com