Point-to-point on-chip communication module based on interruption

A point-to-point communication and communication module technology, which is applied in the direction of instruments, electrical digital data processing, computers, etc., can solve problems such as insufficient parallelism, insufficient utilization, and low communication efficiency, so as to reduce resource consumption, reduce software overhead, and improve The effect of parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

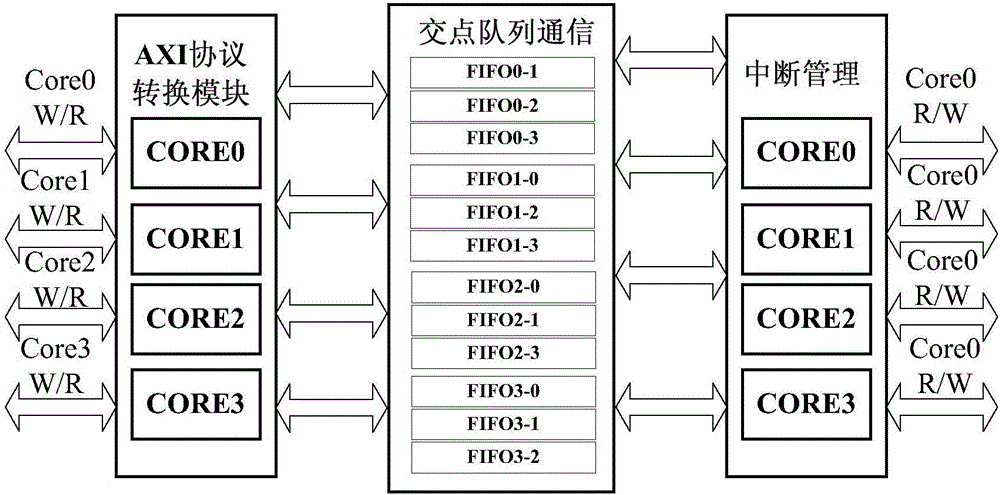

[0033] Overall structure

[0034] Such as figure 1 It is a schematic diagram of the overall structure. The interrupt-based point-to-point on-chip communication module is a 4X4 array structure, which consists of three parts: AXI protocol conversion module, intersection queue communication module and interrupt management module. Its data flow is as follows:

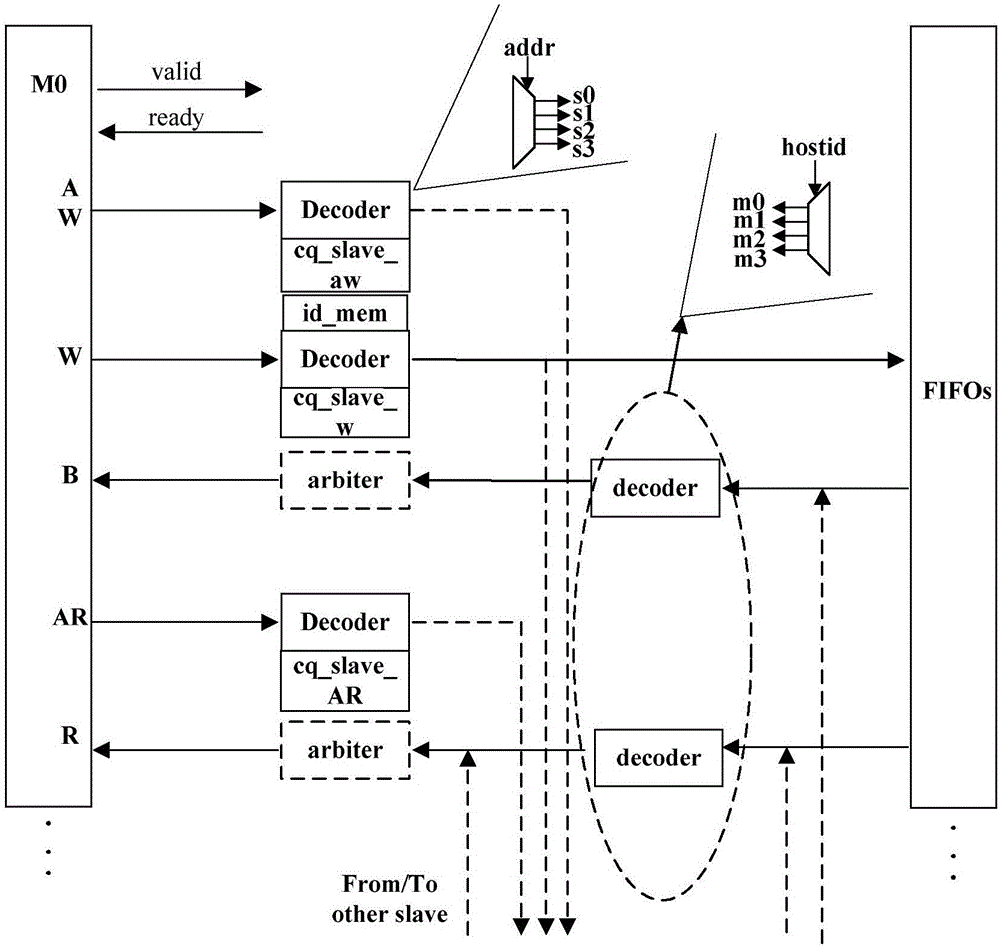

[0035] Take Core0 sending data to Core1 as an example (other inter-core communication processes are similar), the sent data is decoded by the AXI protocol conversion module, and then stored in the corresponding FIFO0-1 cache. To solve the problem of head blocking, use The virtual channel structure (as shown in the system structure diagram...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com