High-avalanche capability power semiconductor transistor structure and preparation method thereof

A technology for power semiconductors and avalanche tolerance, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as increased fluctuations in process preparation, increased device manufacturing costs, and poor breakdown uniformity. Eliminate the impact of process fluctuations on devices, reduce production costs, and improve avalanche tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

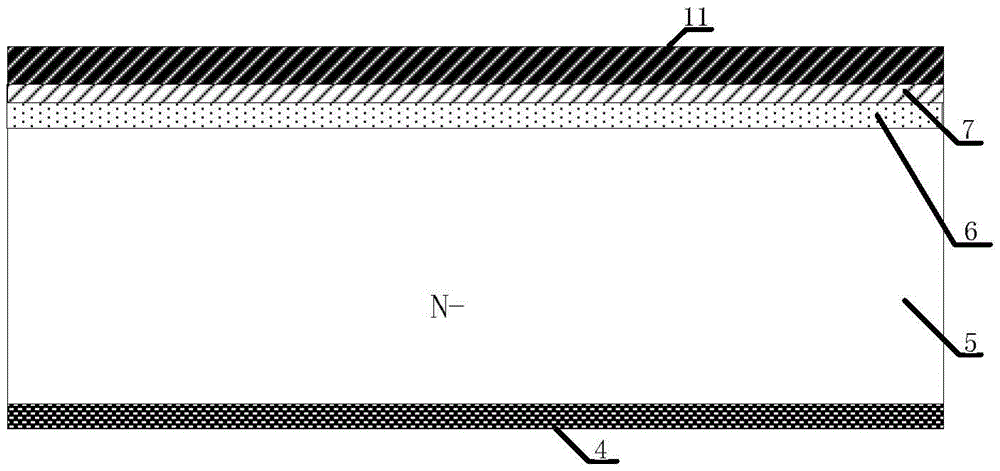

[0035] A power semiconductor transistor structure with high avalanche tolerance, comprising an N-type substrate 4 serving as a drain region, an N-type epitaxial layer 5 is arranged on the N-type substrate 4, and a P-type epitaxial layer 5 is arranged on the surface of the N-type epitaxial layer 5. The strip-shaped body region 6, the surface of the P-type strip-shaped body region 6 is provided with a heavily doped N-type source region 8 and a heavily doped P-type source region 7, and an insulating gate oxide layer 10 is arranged on the N-type epitaxial layer 5. Conductive polysilicon 11 is provided on the insulating gate oxide layer 10, except for the heavily doped P-type body region 7 and part of the heavily doped N-type source region 8, the conductive polysilicon 11 exists above the surface of the N-type epitaxial layer 5, so An insulating dielectric layer 9 is provided on the conductive polysilicon 11, and a source metal 12 is connected to the heavily doped P-type body region...

Embodiment 2

[0040] A method for preparing a power semiconductor transistor structure with high avalanche resistance according to claim 1, characterized in that:

[0041] The first step: first select heavily doped N-type silicon material as the N-type substrate 4, and epitaxially grow the N-type epitaxial layer 5, the thickness of the N-type epitaxial layer 5 is about 50 μm, and the resistivity is about 13ohm*cm - 3 ~18ohm*cm - 3 ;

[0042] Step 2: Deposit photoresist on the N-type epitaxial layer 5 and etch, then ion-implant boron, the implantation dose is about 1×10 13 cm - 3 ~1×10 14 cm - 3 , and high-temperature (above 1000° C.) annealing to form multiple P-type bow body regions 13;

[0043] Step 3: Thermally oxidize on the N-type epitaxial layer 5 to form an insulating gate oxide layer 10, then deposit conductive polysilicon 11 on the silicon dioxide, then deposit photoresist and etch away a part of the conductive polysilicon and silicon dioxide, through self-aligned ion imp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com