Semiconductor structure and manufacture method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of semiconductor structure performance that need to be improved, so as to eliminate the problem of bonding offset and reduce adverse effects Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] It can be seen from the background art that the performance of the semiconductor structure formed in the prior art needs to be improved.

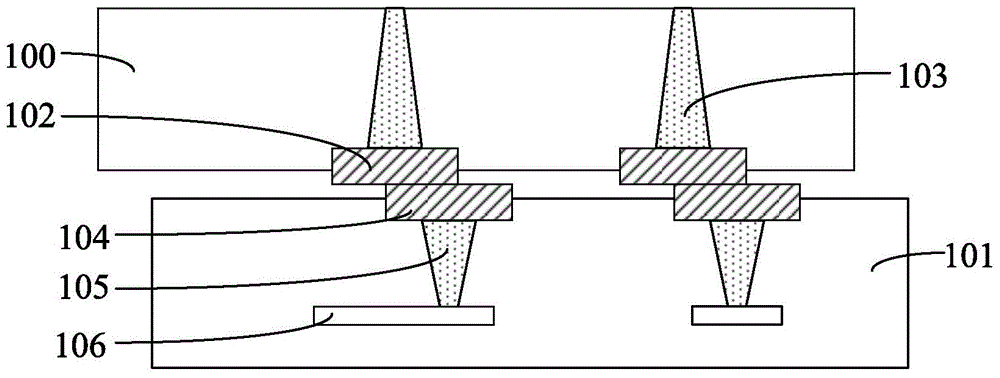

[0038] Please refer to figure 1 , in one embodiment, a first wafer 100 is provided, the first wafer 100 has a first plug 103 inside, and the first wafer 100 is also formed with a first plug electrically connected to the first plug 103. A metal layer 102, and the top of the first metal layer 102 is higher than the surface of the first wafer 100; a second wafer 101 is provided, and a second plug 105 is provided in the second wafer 101. A second metal layer 104 electrically connected to the second plug 105 is also formed in the circle 101 , and the top of the second metal layer 104 is higher than the surface of the second wafer 101 .

[0039] Please continue to refer figure 1 , performing an alignment process on the first wafer 100 and the second wafer 101, and then performing a bonding process on the first wafer 100 and the second wa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com