Method for forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve the problems of poor quality of stress layer and increased difficulty of stress layer, and achieve stable electrical performance and good quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] As mentioned in the background art, as the process nodes of semiconductor devices continue to shrink, the size of the gate structure and the distance between adjacent gate structures also continue to shrink, making it more difficult to form a stress layer, and the quality of the formed stress layer worse.

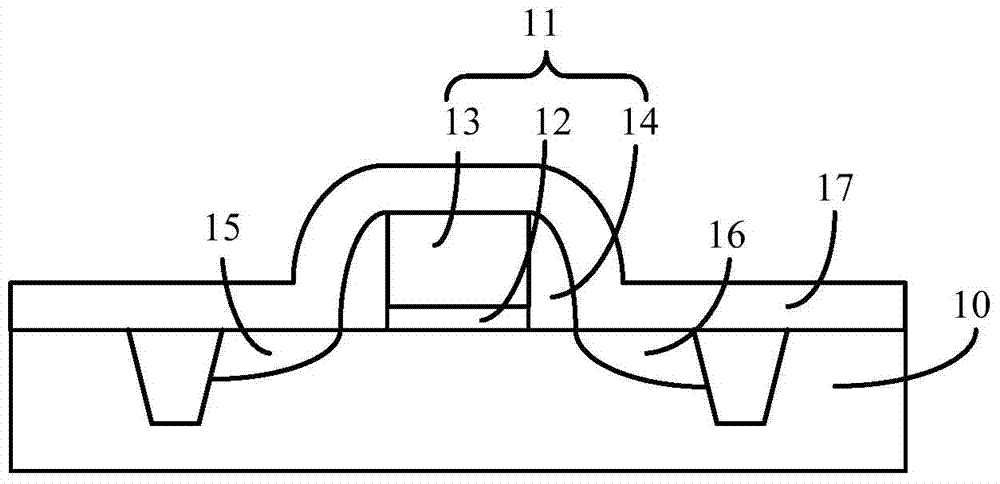

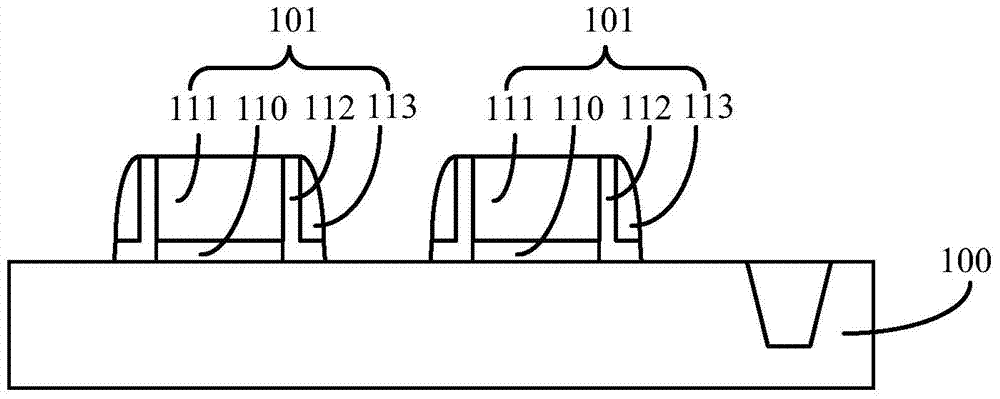

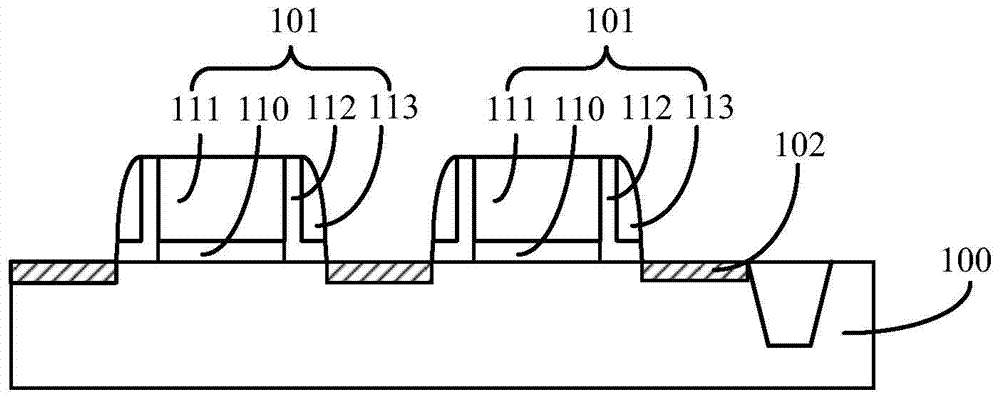

[0035] In order to expand the distance between adjacent gate structures and make the stress layer easy to fill the substrate surface between adjacent gate structures, a solution is to remove part of the sidewall (such as figure 1 shown) to increase the distance between adjacent gate structures, thereby reducing the aspect ratio (Aspect Ratio) of the trench between adjacent gate structures. Such as Figure 2 to Figure 5 Shown is a schematic cross-sectional structure diagram of the formation process of a transistor with a stress layer.

[0036] Please refer to figure 2 , provide a substrate 100, the surface of the substrate 100 has a plurality of gate structures 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com