PMOS device and preparation method thereof

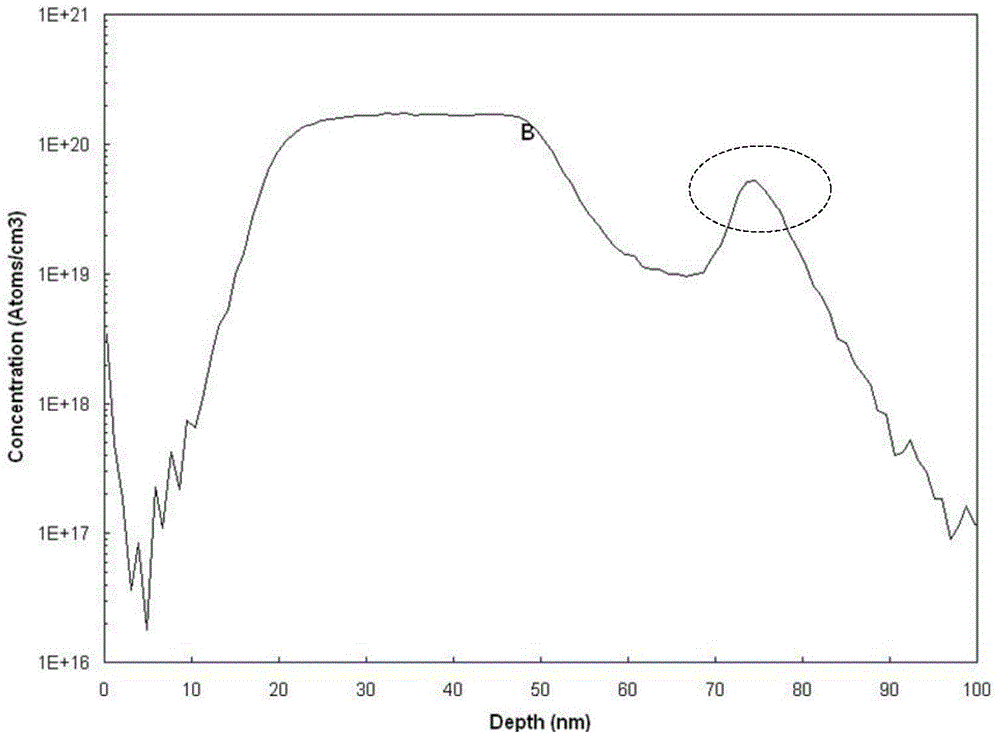

A device and seed layer technology, applied in the field of semiconductor technology, can solve the problems of device performance degradation, aggregation interface, easy to generate defects, etc., and achieve the effect of reducing resistance, uniform distribution, and improving hole mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

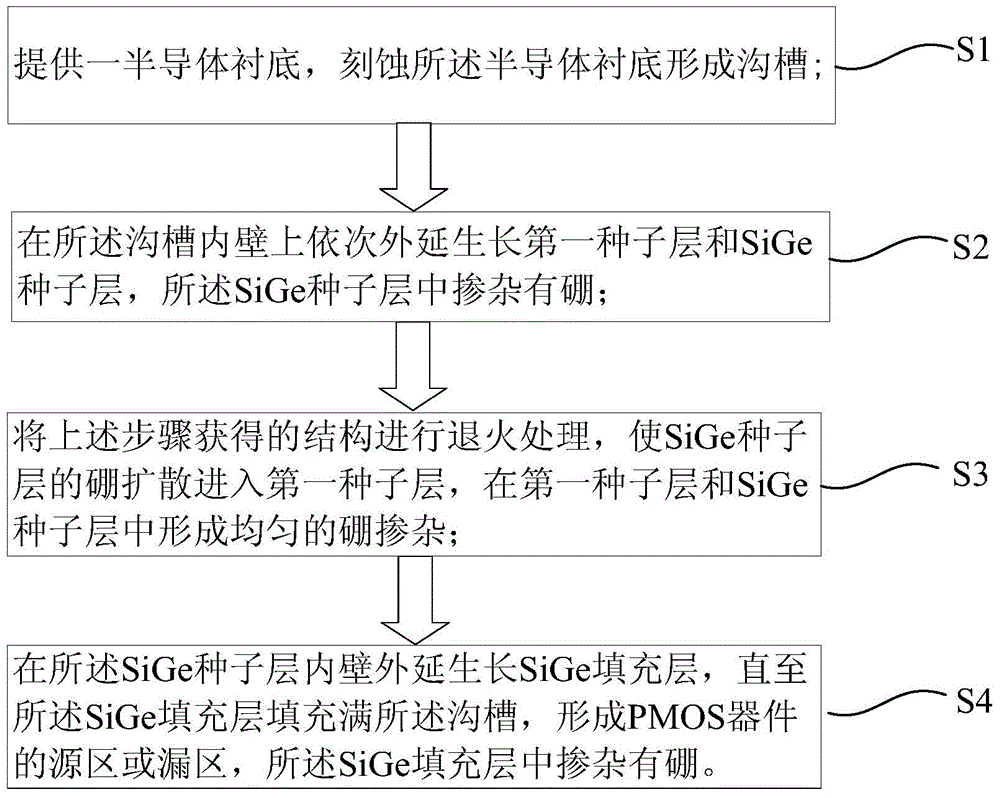

[0044] Such as figure 2 As shown, the present invention provides a kind of preparation method of PMOS device, and the preparation method of described PMOS device comprises the following steps at least:

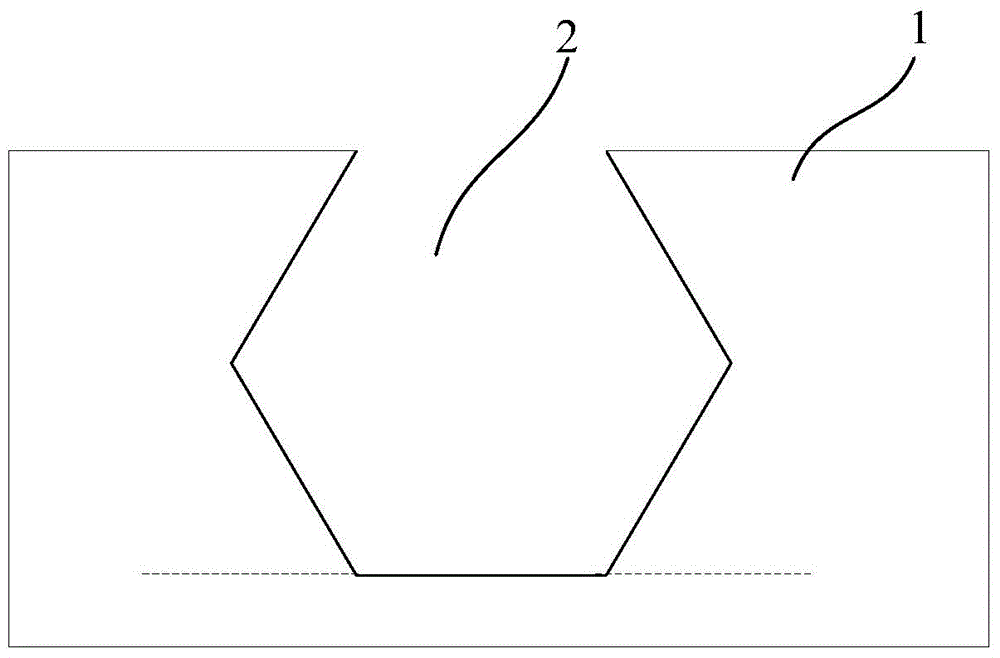

[0045] First execute step S1, such as image 3 As shown, a semiconductor substrate 1 is provided, and the semiconductor substrate is etched to form a trench 2 .

[0046] The semiconductor 1 substrate can be any known semiconductor substrate, including but not limited to Si substrate or SOI substrate. In this embodiment, the semiconductor substrate 1 is described by taking a Si substrate as an example.

[0047]The trench 2 can be formed by using known techniques, for example, dry etching, wet etching and the like. The shape of the trench 2 formed includes but not limited to a sigma shape, ie a “Σ” shape. Certainly, the groove 2 may also be in the shape of a rectangle, an inverted trapezoid, etc. as required. In this embodiment, the shape of the trench 2 is a “Σ” shape to ...

Embodiment 2

[0073] The present invention also provides a PMOS device, which is made by the preparation method in Embodiment 1, such as Figure 6 As shown, the PMOS device includes at least:

[0074] A semiconductor substrate 1, in which a trench 2 is formed by etching;

[0075] A first seed layer 3 containing uniform boron doping is epitaxially extended on the inner wall of the trench 2;

[0076] A SiGe seed layer 4 containing uniform boron doping is epitaxial on the inner wall of the first seed layer 3;

[0077] The SiGe filling layer 5 is epitaxial on the inner wall of the SiGe seed layer 4 and fills the trench 2 , and the SiGe filling layer 5 is doped with boron.

[0078] Preferably, the groove 2 is in a "Σ" shape. Certainly, the groove 2 may also be in the shape of a rectangle, an inverted trapezoid, etc. as required. In this embodiment, the shape of the trench 2 is a “Σ” shape to enhance the compressive stress effect of the SiGe filling layer subsequently formed in the trench 2 ....

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com