XNOR-XOR double-rail pre-charge logic unit

A logic unit and pre-charging technology, applied in the field of circuit electronics, can solve problems such as large-area overhead and DRP logic security threats, and achieve the effects of balancing power consumption, solving early propagation effects, and eliminating memory effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

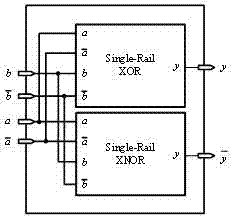

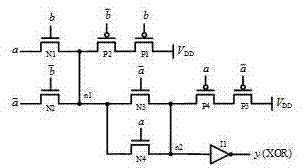

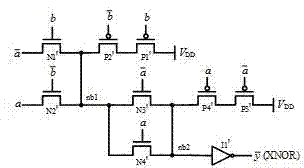

[0022] From figure 1 , figure 2 and image 3 It can be seen that the NOR-XOR dual-rail precharge logic unit of the present invention includes a single-rail NOR circuit part and a single-rail XOR circuit part.

[0023] The single-rail XOR logic circuit part is composed of NMOS transistor N1, NMOS transistor N2, NMOS transistor N3, NMOS transistor N4, PMOS transistor P1, PMOS transistor P2, PMOS transistor P3, PMOS transistor P4 and inverter I1.

[0024] The source of NMOS transistor N1 is connected to the input signal a , the gate is connected to the input signal b ; The source of NMOS transistor N2 is connected to the input signal , the gate is connected to the input signal ; At the same time, the drains of the NMOS transistor N1 and the NMOS transistor N2 are short-circuited.

[0025] The PMOS transistor P1 is connected in series with the PMOS transistor P2, wherein the source of the PMOS transistor P1 is connected to the power supply V DD , the gate is connected t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com