Method for forming gate electrode

A gate and dummy gate technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of poor performance of MOS transistors and affecting the shape of metal gates, etc., and achieve the effect of easy control of width and formation position

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

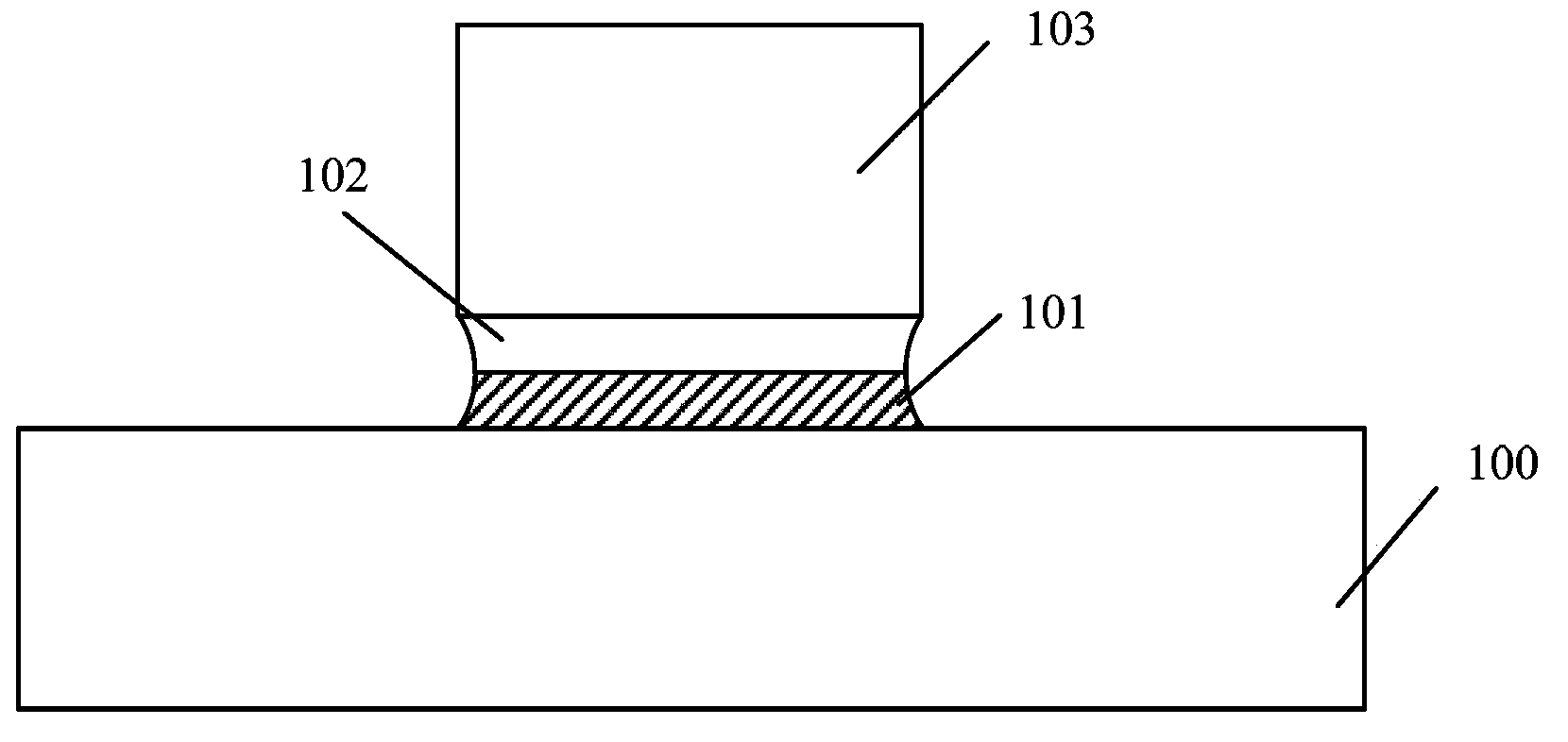

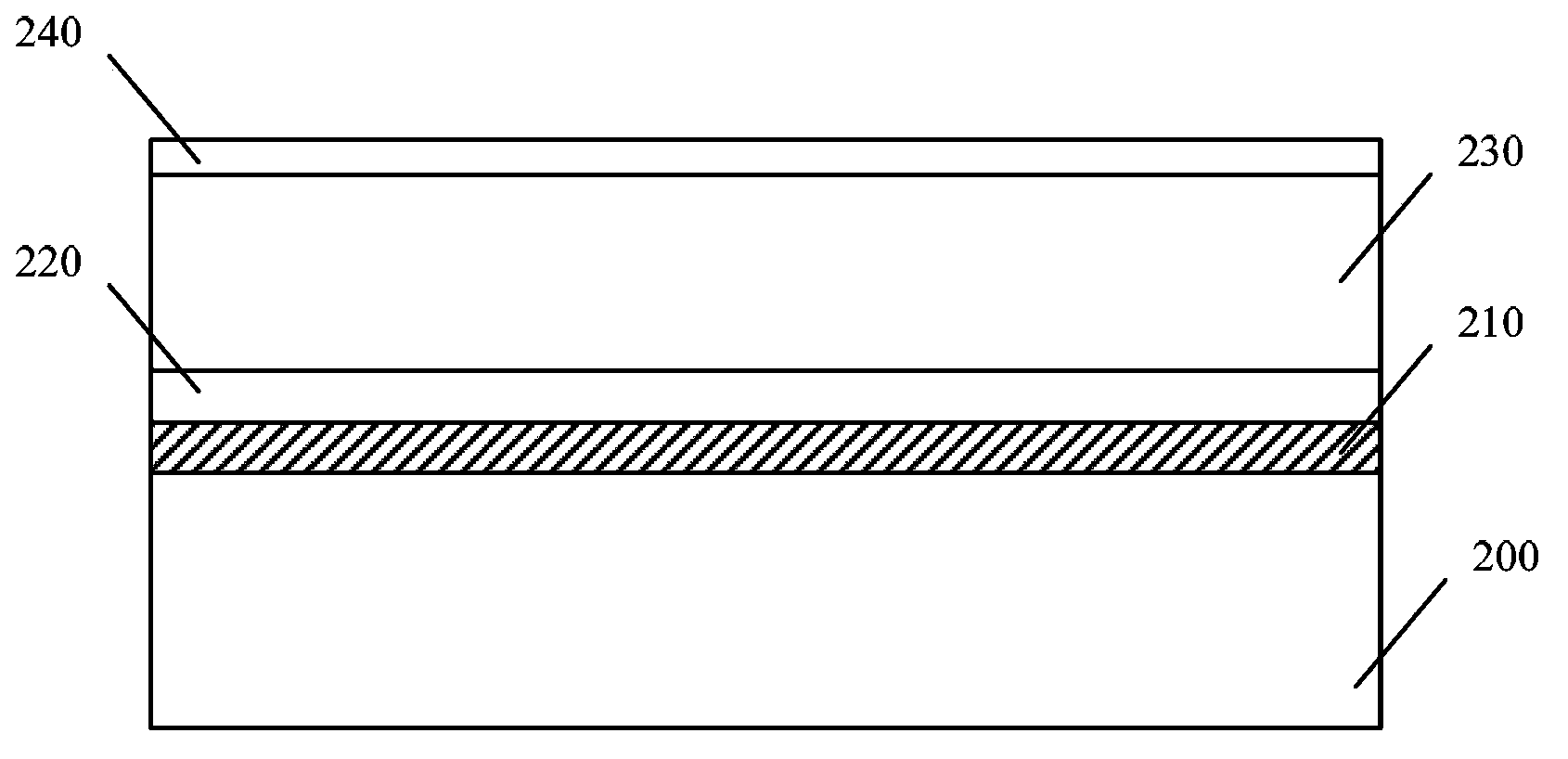

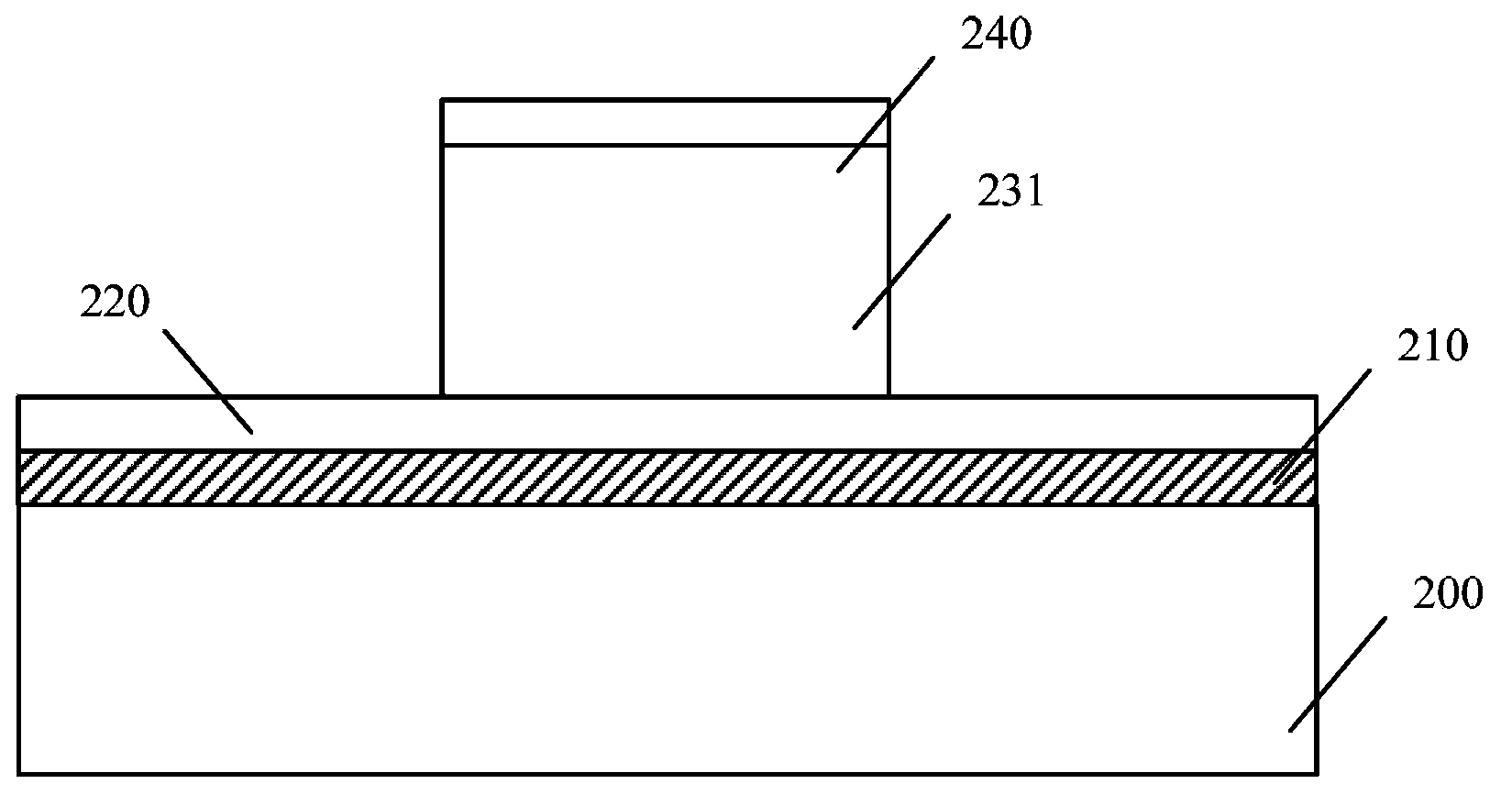

[0036] Figure 2 to Figure 8 is a schematic cross-sectional structure diagram of the formation process of the gate in the first embodiment of the present invention.

[0037] Please refer to figure 2 A semiconductor substrate 200 is provided, the surface of the semiconductor substrate 200 has a gate dielectric material layer 210 , the gate dielectric material layer 210 has a protective material layer 220 thereon, and the protective material layer 220 has a dummy gate material layer 230 thereon.

[0038] The semiconductor substrate 200 may be silicon or silicon-on-insulator (SOI), and the semiconductor substrate 200 may also be germanium, silicon germanium, gallium arsenide, or germanium-on-insulator. In this embodiment, the semiconductor substrate 200 is a silicon substrate. The semiconductor substrate 200 serves as a working platform for subsequent processes.

[0039] The surface of the semiconductor substrate 200 has a gate dielectric material layer 210, the gate dielectr...

no. 2 example

[0058] Figure 9 to Figure 16 is a schematic cross-sectional structure diagram of the formation process of the gate in the second embodiment of the present invention.

[0059] Please refer to Figure 9 , provide a semiconductor substrate 300, the semiconductor substrate 300 has a first region I and a second region II, the surface of the semiconductor substrate 300 has a gate dielectric material layer 310, and the gate dielectric material layer has a protective material layer 320 , the protective material layer 320 has a dummy gate material layer 330 on it.

[0060] In this embodiment, the dummy gate material layer 330 is a polysilicon layer, the material of the protection layer 320 is a titanium nitride layer, the gate dielectric material layer 310 is a high dielectric constant material, and the high dielectric constant material for HfO 2 , ZrO 2 、Al 2 o 3 , HfSiO, HfSiON, HfTaO and one or more of HfZrO. In this embodiment, a hard mask layer 340 is further formed on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com