Layout legalization method and system for distributed computing of large-scale integrated circuit

A large-scale integrated circuit and distributed computing technology, which is applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as the inability to solve the constraints of wire-network spacing, and achieve the effect of good wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

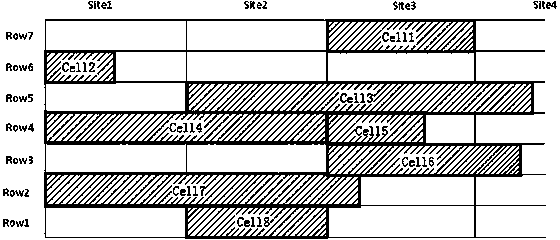

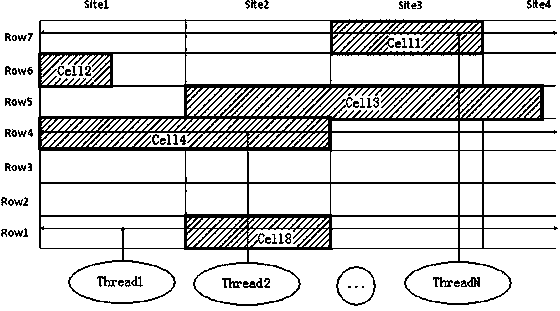

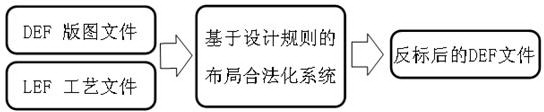

[0028] This embodiment designs a layout legalization method for distributed computing of large-scale integrated circuits. First, a hash lookup table based on bit storage is created to store the required minimum distance between two unit modules in various rotation directions. , secondly divide the entire layout area into independent sub-problems according to the layout rows, and then detect whether the distance constraint is satisfied between two adjacent unit modules for each row, and move or flip the unit pairs that do not satisfy the distance constraint , so that the distance between them satisfies the distance constraint. The problem is to place the unit modules on the entire chip on the specified site in the layout line. In addition to ensuring that the units cannot overlap, it is also necessary to ensure that a certain distance constrai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com