Router Fault Tolerance Method Based on Fault Channel Isolation Detection in Network-on-Chip

An on-chip network and router technology, applied in the field of router fault tolerance based on fault channel isolation and detection, can solve problems such as area and power consumption overhead, and achieve the effects of reducing complexity, reducing fault tolerance overhead, and reducing overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

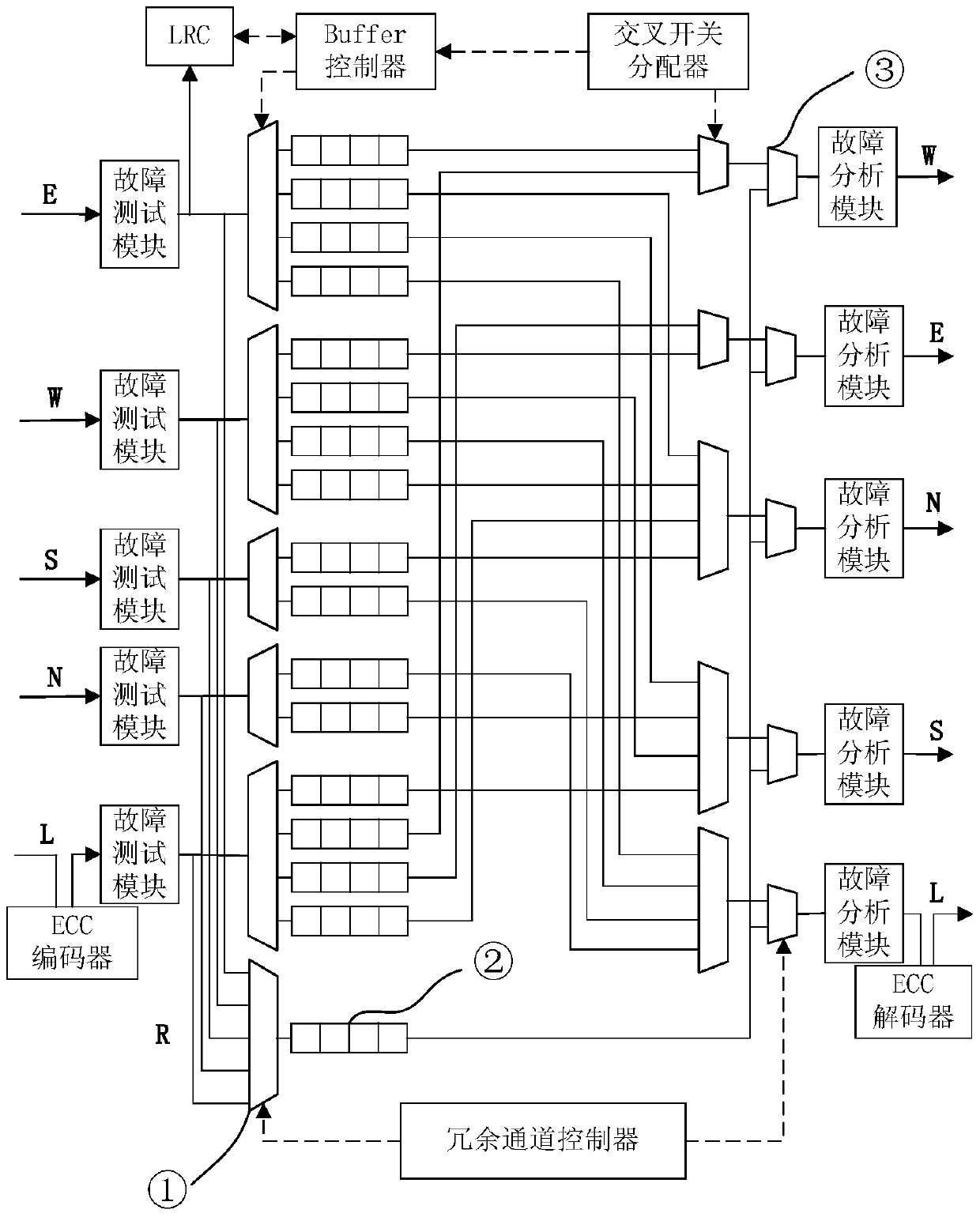

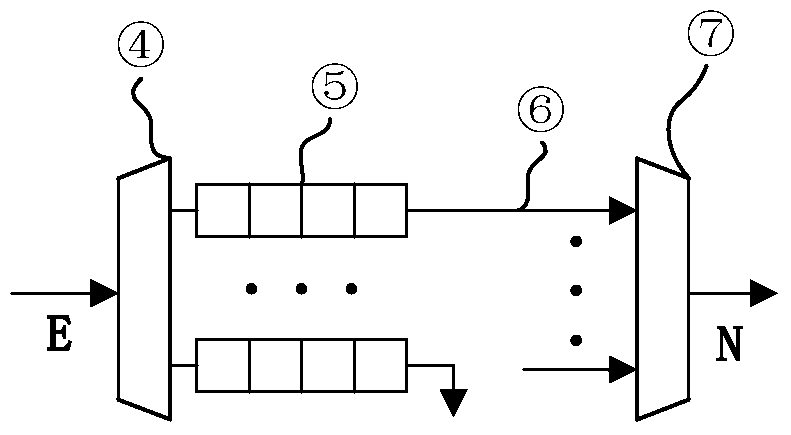

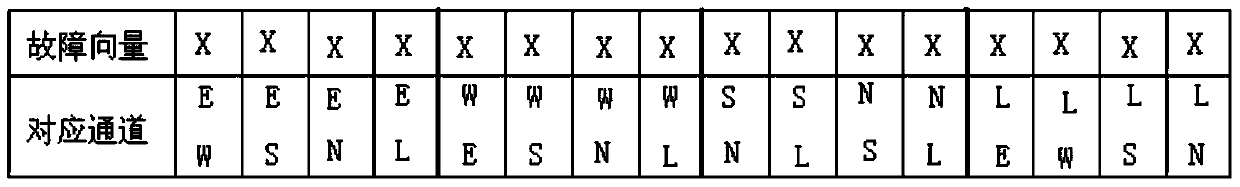

[0035] A router fault-tolerant method based on fault channel isolation detection in a network on chip, the operation steps are as follows:

[0036] a. When a data packet transmission request arrives, query the fault channel vector table to find out the corresponding fault state of the request channel. If the request channel is not faulty, the data packet will be transmitted to the output port through the request channel. If the request channel has a permanent failure, then the The data packet turns to request the redundant channel, and then is transmitted to the output port by the redundant channel;

[0037] b. After the data packet arrives at the output port, ECC detection is performed. If there is no error in the data bit, the data is transmitted normally. If there is a single error in the data bit, it will be automatically corrected and then transmitted. c;

[0038] c. If there is a multi-bit error in the data bit, notify the upstream router to retransmit the data in the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com