Display panel mother board and preparation method thereof

A technology for display panels and motherboards, which is applied in the fields of printed circuit manufacturing, multilayer circuit manufacturing, semiconductor/solid-state device manufacturing, etc., and can solve the problems of inability to release stress, film layer pattern shift, shrinkage or expansion instability And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

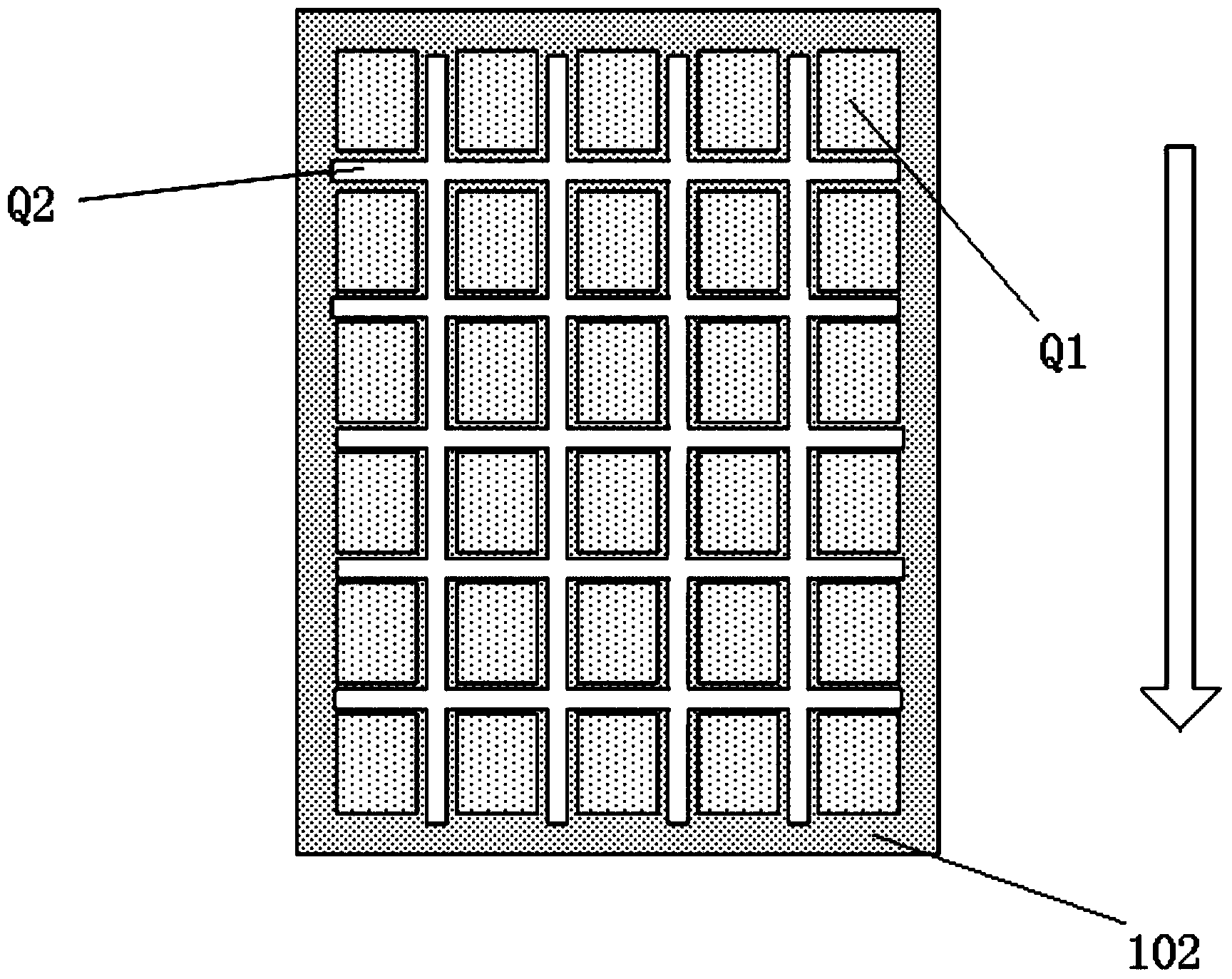

[0026] Such as figure 1 As shown, the present embodiment provides a display panel motherboard, which includes: display panel regions Q1 arranged at intervals, and a pre-cut region Q2 adjacent to the display panel regions Q1. Wherein, the display panel area Q1 corresponds to the location of the display panel, and the pre-cutting area Q2 corresponds to the location of the cutting line. In the motherboard of the display panel, at least part of the electrical insulating layer 102 disposed in the pre-cut area Q2 is removed.

[0027] Since at least part of the electrical insulating layer 102 located in the pre-cut area Q2 in the motherboard of the display panel of this embodiment is removed, the internal stress of the electrical insulating layer 102 can be well released, so that it can be well avoided. The influence of the greater stress inside the electrical insulating layer 102 on other film layers above or below the electrical insulating layer 102 can further affect the deviatio...

Embodiment 2

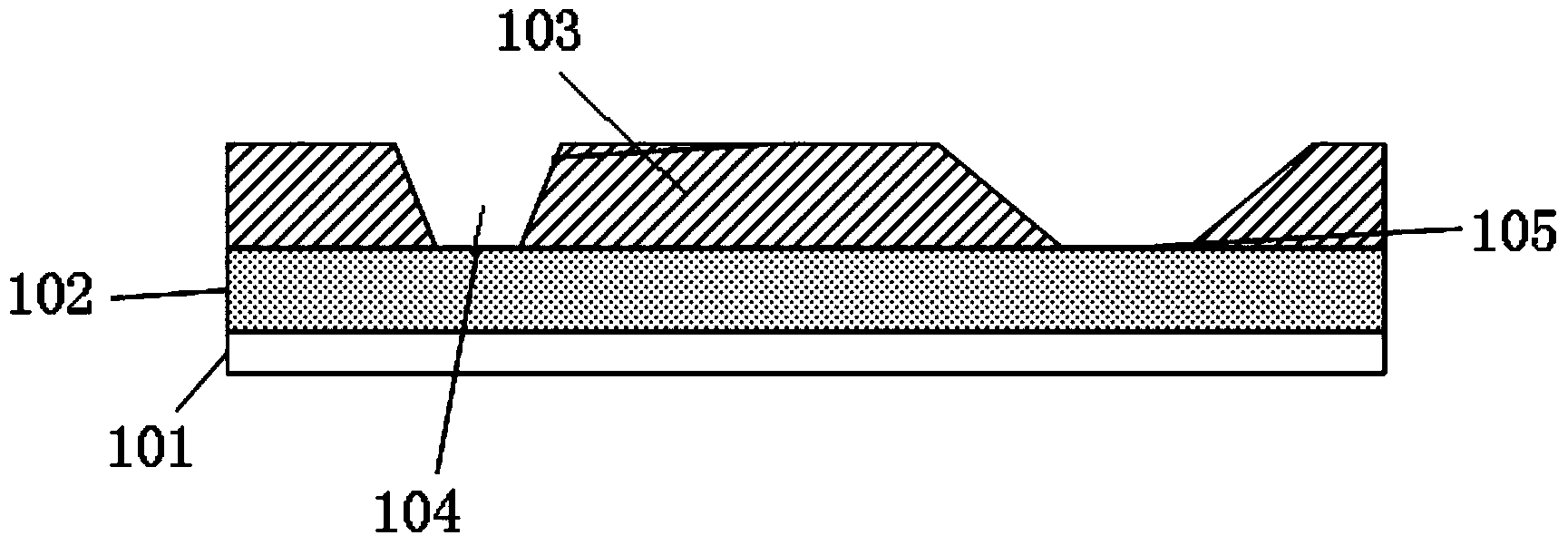

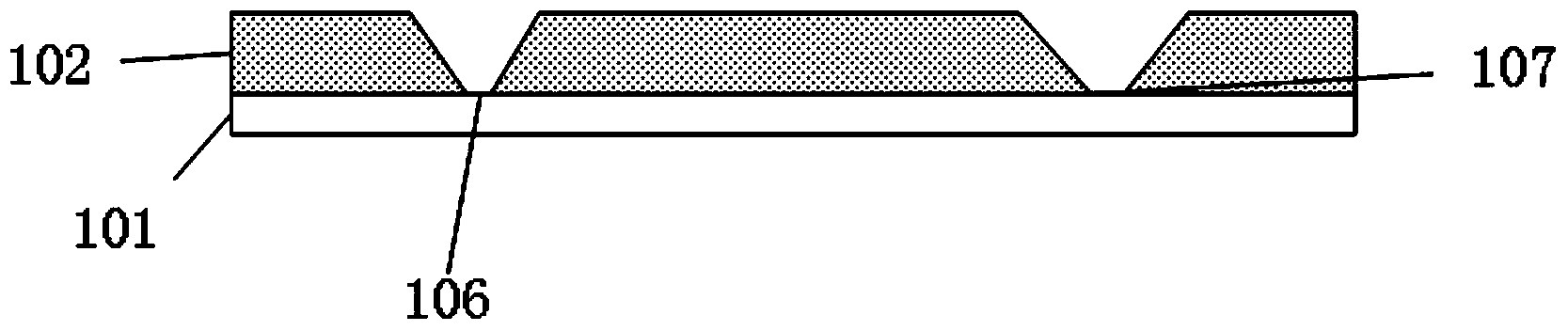

[0032] Such as Figure 2a and 2b As shown, this embodiment provides a method for preparing a display panel motherboard, the display panel motherboard comprising: display panel regions arranged at intervals, and a pre-cut region adjacent to the display panel, which includes the following steps:

[0033] Form a layer of electrical insulation layer film 102 on the substrate 101, and coat photoresist 103 on the electrical insulation layer film 102, expose and develop the photoresist, and contact the photoresist 104 of the via hole area and the electrical field of the pre-cut area. The photoresist 105 in the area where the insulating layer will be removed is removed, such as Figure 2a shown in .

[0034] Certainly, the step of forming contact vias may be synchronized with the above steps, or may be independent. When multiple electrical insulating layers 102 are included, the contact vias of each layer may be formed separately first, and then the electrical insulating layers 102...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com