III-nitride semiconductor device and manufacturing method for same

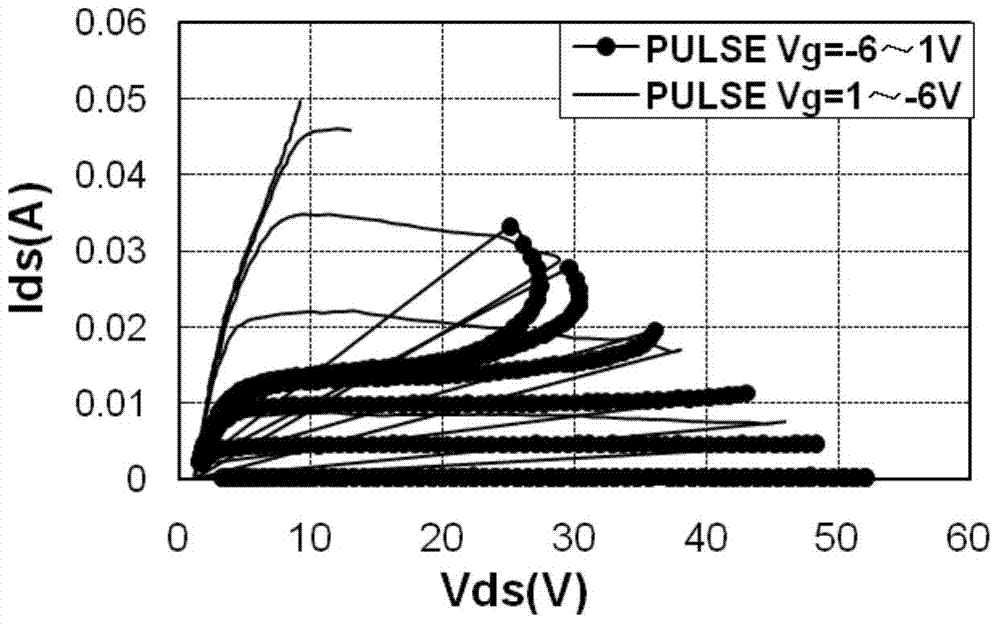

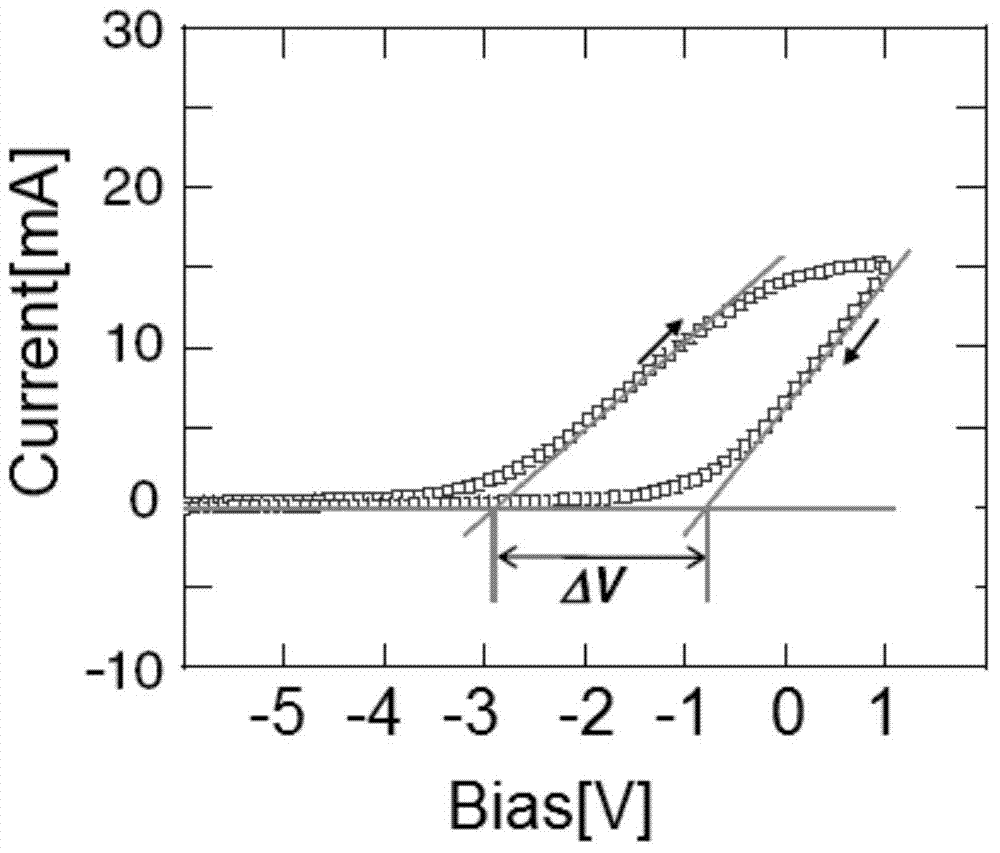

A nitride semiconductor and nitride technology, applied in the field of microelectronics, can solve the problems of non-overlapping forward and reverse curves, current collapse, etc., to reduce the impact of current collapse effect, small gate leakage current, and reduce current The effect of the collapse effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

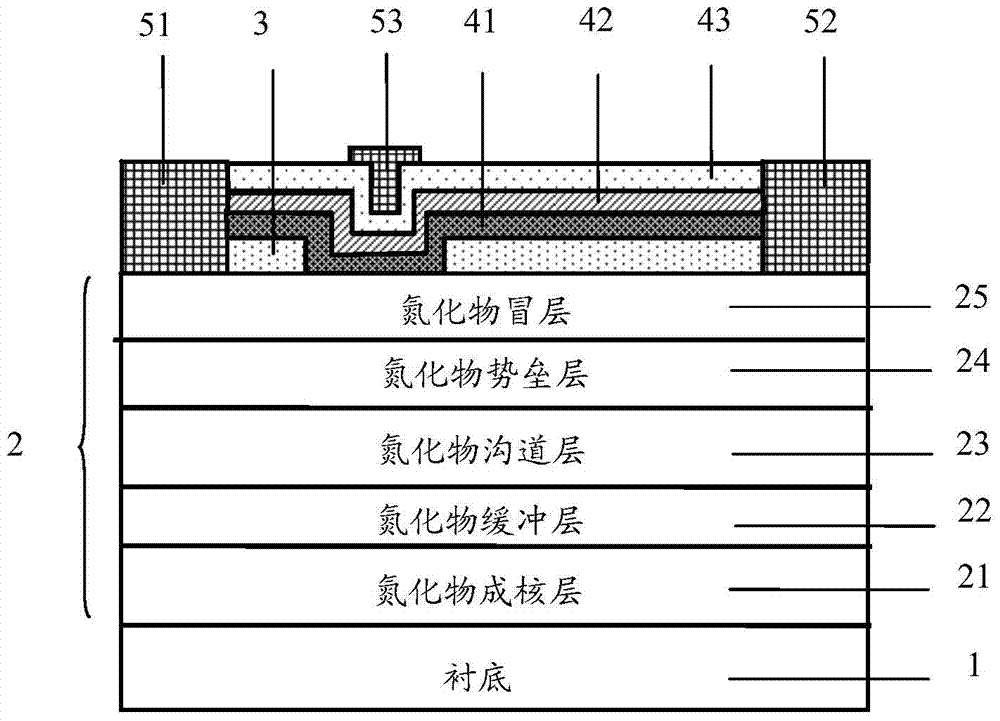

[0054] A group III nitride semiconductor device of the present invention, comprising:

[0055] Substrate;

[0056] A nitride semiconductor layer on the substrate, the nitride semiconductor layer includes a nitride nucleation layer, a nitride buffer layer, a nitride channel layer, and a nitride barrier layer formed sequentially from the direction of the substrate;

[0057] Preferably, a nitride capping layer may also be included between the nitride barrier layer and the passivation layer;

[0058] Preferably, the nitride capping layer includes a gallium nitride layer;

[0059] Preferably, an aluminum nitride insertion layer is provided between the nitride barrier layer and the nitride channel layer;

[0060] The passivation layer on the nitride semiconductor layer, the passivation layer is a combination of one or more of silicon nitride, silicon aluminum nitride, and silicon dioxide, and the passivation layer is etched in the gate region to expose nitrogen a compound barrier...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com