Optimizing time synchronizing device for multi-channel clock sources

A technology of a time synchronization device and a comparator, which is applied in the direction of synchronization device, synchronization, and clock driven by a synchronous motor, etc., can solve the problems of fluctuation of the second pulse time interval, the adverse effect of the stable operation of the merging unit, and the stability of the time synchronization system. , to achieve the effect of small standard deviation and improved reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0024] This embodiment is the basic structure of the present invention.

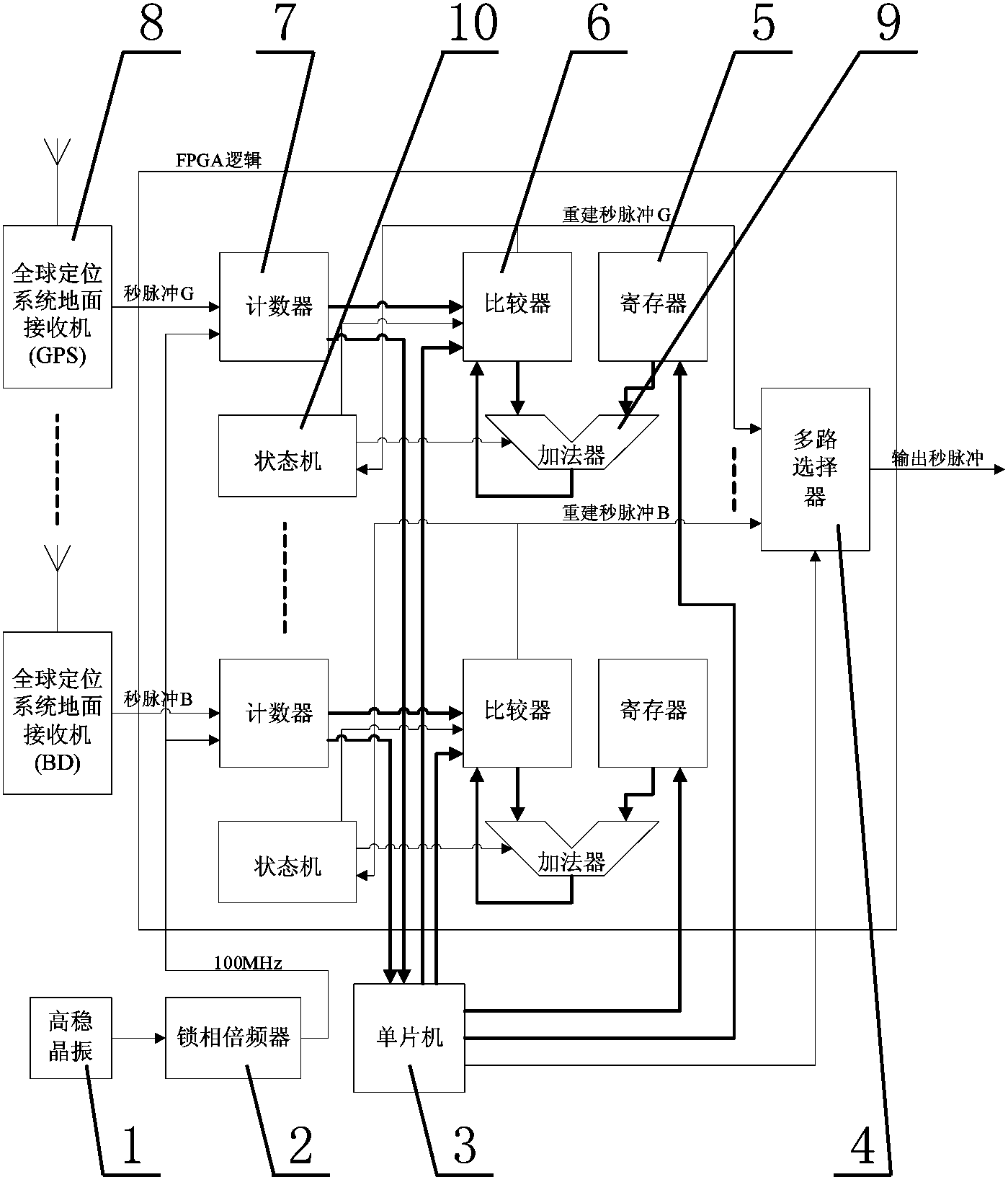

[0025] Such as figure 1 , including a high stability crystal oscillator 1, a single-chip microcomputer 3 and a multiplexer 4; also includes at least two units with the same structure, each unit includes a global positioning system ground receiver 8, a counter 7, a comparator 6 and a register 5, each The second pulse output end of the global positioning system ground receiver 8 in the unit is connected with the event trigger input end of the counter 7, and the count value output end of the counter 7 is connected with the input end of the comparator 6 in the unit, and the built-in value of the comparator 6 For comparison, when the values are the same, the comparator 6 outputs a pulse signal to the multiplexer 4 . The clock output end of the high-stable crystal oscillator 1 is directly connected to the clock input end of the counter 9 in each unit or connected through a phase-locked frequency multiplier ...

Embodiment 2

[0027] This embodiment is a specific optimized structure of the present invention. Such as figure 2 , on the basis of the first embodiment, each unit further includes a state machine 10 and an adder 9 . The input end of state machine 10 is connected to the output end of comparator 6, and comparator 6 is used to start the state cycle of state machine 10; An output end of state machine 10 is connected with the control end of adder 9, is used to start adder 9, the other output terminal of the state machine 10 is connected to the writing control terminal of the comparator 6 to control the writing of the output of the adder 9 into the comparator 6.

[0028] The two input terminals of the adder 9 are respectively connected with the output port of the comparator 6 and the register 5, and are used to add the built-in value of the comparator 6 to the value of the register 5, and the output port of the adder 9 is connected with the data input of the comparator 6. The port is connecte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com