Manufacturing method of self-aligned insulated gate bipolar transistor

A technology of bipolar transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the size of the emission area of lithography precision cannot be reduced, and achieve the reduction of strict alignment times of lithography, and the device Effect of small structure size and reduced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] A method for manufacturing a self-aligned insulated gate bipolar transistor, comprising the steps of:

[0070] A. A crystalline silicon substrate of the first conductivity type is provided as the base region of the first conductivity type;

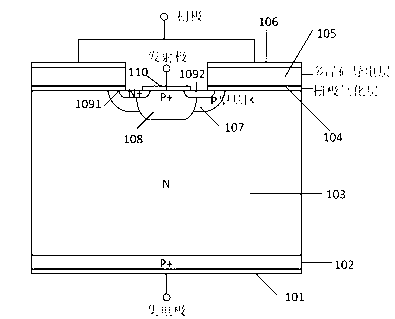

[0071] There are two types of conductivity, one is N-type conductivity, and the other is P-type conductivity. The first conductivity type mentioned here is any one of them, and the second conductivity type is another one. The base region of the first conductivity type is located at the carrier diffusion region 103 .

[0072] B. making a first insulating layer on the front side of the crystalline silicon substrate;

[0073] Here, the first insulating layer refers to the first insulating layer to be processed. The position of the first insulating layer is at the gate oxide layer 104 . Available materials include insulating materials such as silicon oxide, silicon nitride, and aluminum oxide.

[0074] C. Depositing a polysilicon gat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com