Flow compilation optimization method oriented to chip multi-core processor

A multi-core processor and optimization method technology, applied in the field of computer compilation, can solve the problem that the compilation optimization method does not optimize the architecture characteristics of chip multi-core processors, does not make full use of system hardware resources, program execution efficiency, and does not take into account the allocation of processing core storage Optimization problems and other issues to achieve the effect of reducing communication overhead, reducing overhead, and improving execution performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

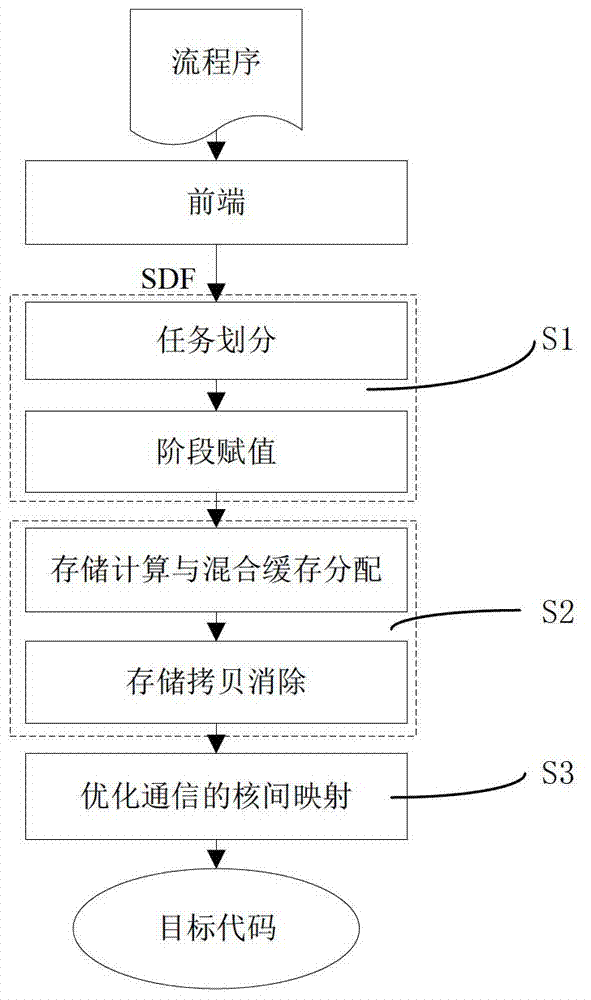

[0021] Such as figure 1 Shown is the structural frame diagram of this embodiment in the stream compilation system. After the stream program is parsed by the front end of the stream compiler, an intermediate representation—a synchronous data flow graph will be generated, and then it will go through software pipeline scheduling, storage access optimization, and communication optimization in sequence. level optimization process, and finally generate the object code and complete the compilation.

[0022] (1) Software pipeline scheduling

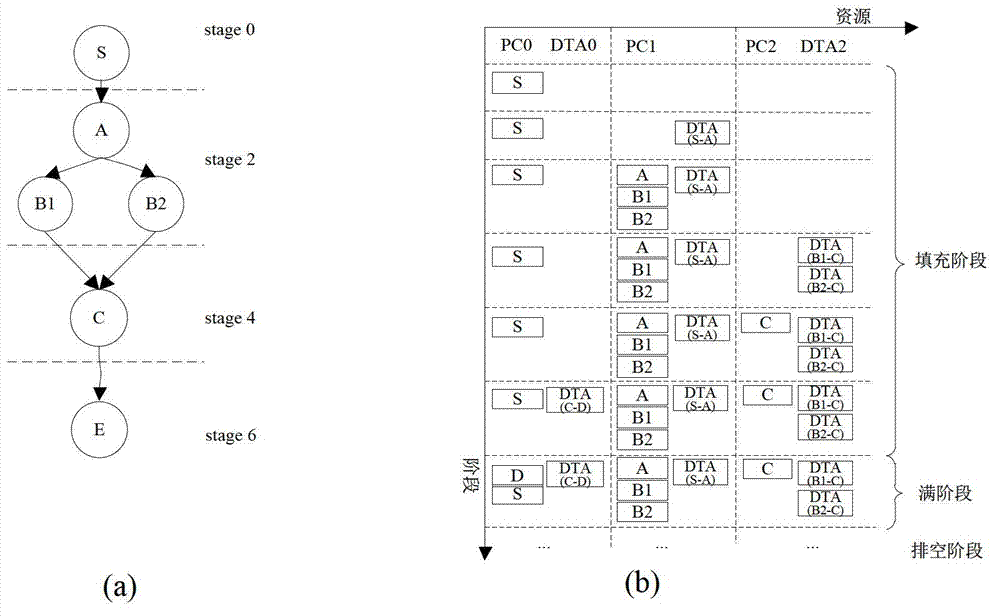

[0023] This step includes three sub-steps: division of tasks, allocation of stages and construction of a pipeline schedule. The integer linear programming problem is used to model the task division problem of the flow program. The model takes the calculation amount of the nodes in the synchronous data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com