Method for realizing parallel Turbo code interweaver and used in LTE (Long Term Evolution)

An implementation method and interleaver technology, applied in the field of Turbo coding and long-term evolution technology, can solve problems such as shortening the coding time of large code blocks, poor operability, and uncertain number of clocks, and achieve the elimination of adverse effects and modulo calculations Simplified, easy-to-design effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

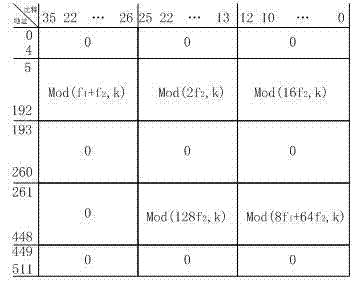

[0033] According to the 3GPP TS 36.212 V10.0.0 protocol, the Turbo code interleaver function is defined as:

[0034] ∏(i)=mod((f 1 i+f 2 i 2 ), k) wherein i=0, 1, . . . , k-1k is the code block length.

[0035] From this you can get:

[0036] ∏(i+8)=mod(f 1 (i+8)+f 2 (i+8) 2 ,k)

[0037] ∏(i+8)=mod(∏(i)+mod(mod(8f 1 +64f 2 , k)+mod(16if 2 , k), k), k)

[0038] The above expression is still not convenient for FPGA implementation, because the recursive relation contains a variable item with i, if mod(16f 2 , k) is not 0, as i increases, for mod(16if 2, the modulo operation of k) becomes more and more difficult, and the number of clocks required also becomes uncertain, so there is no substantial improvement for the realization of FPGA, and as the code block length becomes larger, the performance will be sharp becomes worse, and this is the opposite of the original intention of shortening the encoding time of large code blocks, so if this step is used as the final rel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com