Method for preparing organic field effect transistor structure

A technology of transistors and organic fields, applied in the field of organic electronics, can solve problems such as complex processes and mutual interference of modifiers, and achieve the effects of improving growth quality, mobility and injection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

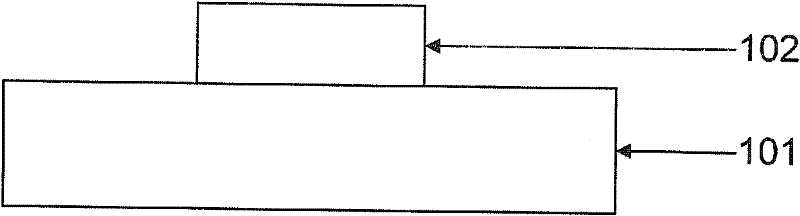

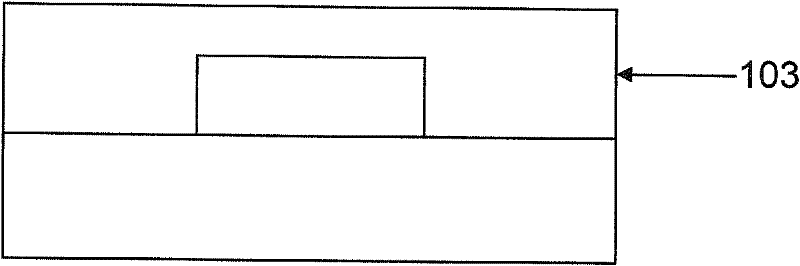

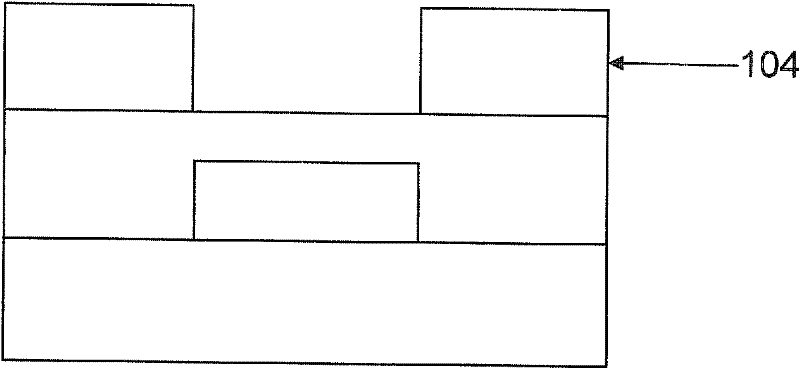

[0032] Figure 1-1 to Figure 1-5 A flow chart of the method for preparing an organic field effect transistor structure provided by the present invention, the method mainly includes the following steps:

[0033] Such as Picture 1-1 As shown, a patterned gate electrode 102 is prepared on an insulating substrate 101, and the film deposition methods of the gate electrode layer include vacuum thermophysical deposition, electron beam deposition, ion-assisted deposition, sputtering, inkjet printing, and spin coating. Wherein the insulating substrate 101 is the supporting part of the electrode, the gate dielectric and the organic semiconductor thin film layer, and the substrate should have a relatively low surface roughness, and a certain ability of waterproofing and oxygen penetration. Including silicon wafers with insulating films such as silicon oxide and silicon nitride, insulating glass and insulating plastic films. The material of the thin film of the gate electrode 102 includ...

Embodiment

[0039] The specific preparation method of the organic field effect transistor provided by this embodiment is as follows:

[0040] Step 1, on the silicon wafer substrate with 300nm silicon oxide, first prepare the photoresist pattern of the gate electrode by photolithography process, and then deposit a layer of 100nm thick aluminum metal film by electron beam evaporation, and remove the undesired metal film by metal lift-off process. Photoresist and metal film are required to form a patterned aluminum metal gate electrode.

[0041] In step 2, a 30nm-thick aluminum oxide film is prepared as a gate dielectric on the aluminum metal gate electrode by atomic layer deposition technology.

[0042] Step 3, on the surface of the first type of gate dielectric layer, first prepare the photoresist pattern of the source and drain electrodes by photolithography, and then deposit a 50nm thick gold metal film by electron beam evaporation, and remove the unnecessary light through the stripping ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com