Array substrate and manufacturing method thereof as well as display equipment

A technology of an array substrate and a manufacturing method, which is applied in the field of display manufacturing, can solve problems such as low aperture ratio of unit pixels, and achieve the effects of increasing the aperture ratio, reducing the width and increasing the area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

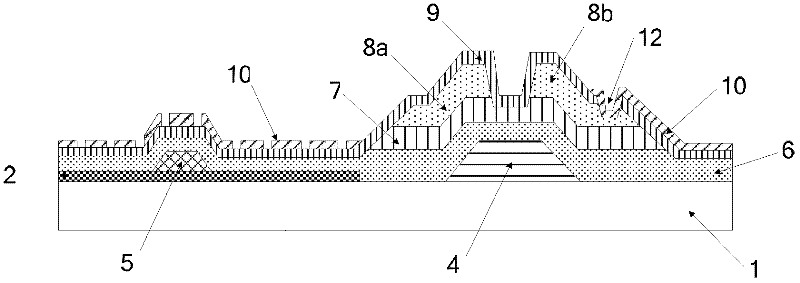

[0055] like figure 2 As shown, in this embodiment, the array substrate includes: a substrate 1; a common electrode 2 formed on the substrate; an insulating layer 3 covering the common electrode 2 and extending to the substrate 1, and the insulating layer 3 covering the common electrode 2 The first via hole 11 is opened in the part; the gate electrode 4 and the common electrode line 5 formed on the insulating layer 3, that is, the common electrode line 5 and the gate electrode 4 are arranged on the same layer, and the common electrode line 5 is located in the first via hole Above 11, the common electrode line 5 is connected to the common electrode 2 through the first via hole 11; the gate electrode protection layer (i.e. gate insulating layer) 6, the gate electrode protection layer 6 connects the gate electrode 4, the common electrode line 5 and the insulating layer 3 completely covered; the active layer 7 formed on the gate electrode protection layer 6; the source electrode 8...

Embodiment 2

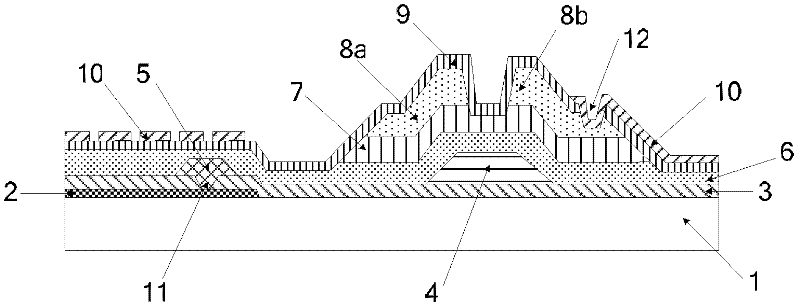

[0066] like image 3 As shown, in this embodiment, the array substrate includes: a substrate 1; a gate electrode 4 and a common electrode line 5 formed on the substrate 1, that is, the common electrode line 5 and the gate electrode 4 are arranged on the same layer; And cover the insulating layer 3 of the gate electrode 4 and the common electrode line 5, the part of the insulating layer 3 covering the common electrode line 5 has a first via hole 11, and the first via hole 11 is located above the common electrode line 5; The common electrode 2 formed on the insulating layer 3, the common electrode 2 is located above the first via hole 11, and the common electrode 2 is connected to the common electrode line 5 through the first via hole 11; completely covering the common electrode 2 and the insulating layer 3 Gate electrode protective layer 6; active layer 7 formed on gate electrode protective layer 6 above gate electrode 4; source electrode 8a and drain electrode 8b formed on act...

Embodiment 3

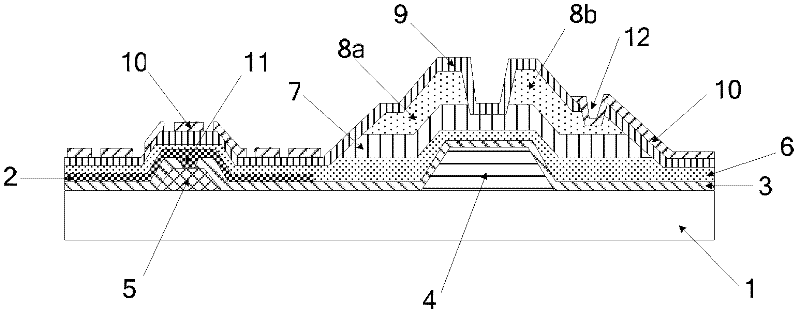

[0075] like Figure 4 As shown, in this embodiment, the array substrate includes: a substrate 1; a gate electrode 4 and a common electrode line 5 formed on the substrate 1, that is, the common electrode line 5 and the gate electrode 4 are arranged on the same layer; The insulating layer 3 that covers the gate electrode 4 and the common electrode line 5; the common electrode 2 formed on the insulating layer 3, the common electrode 2 is located above the common electrode line 5; the gate electrode that completely covers the common electrode 2 and the insulating layer 3 protective layer 6; an active layer 7 formed on the gate electrode protective layer 6 above the gate electrode 4; a source electrode 8a and a drain electrode 8b formed on the active layer 7; covering the source electrode 8a and the drain electrode 8b and extending to The passivation layer 9 on the gate electrode protection layer 6, the part of the passivation layer 9 covering the drain electrode 8b has a second vi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com