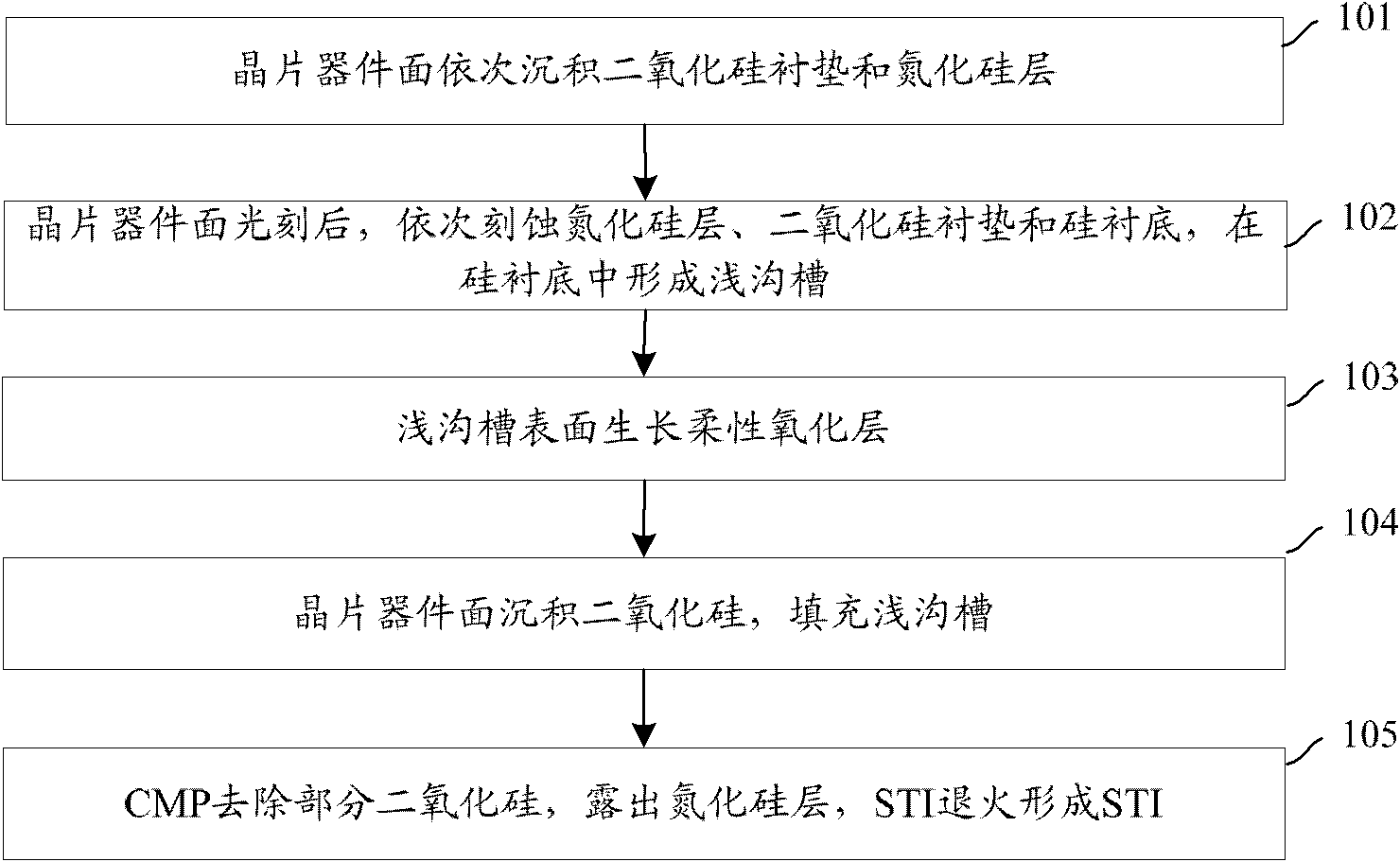

Manufacturing method of STI (shallow trench insulation)

A manufacturing method and technology of shallow trenches, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as boron ion concentration reduction and impact on NMOS device performance, and achieve the effect of avoiding threshold voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution, and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

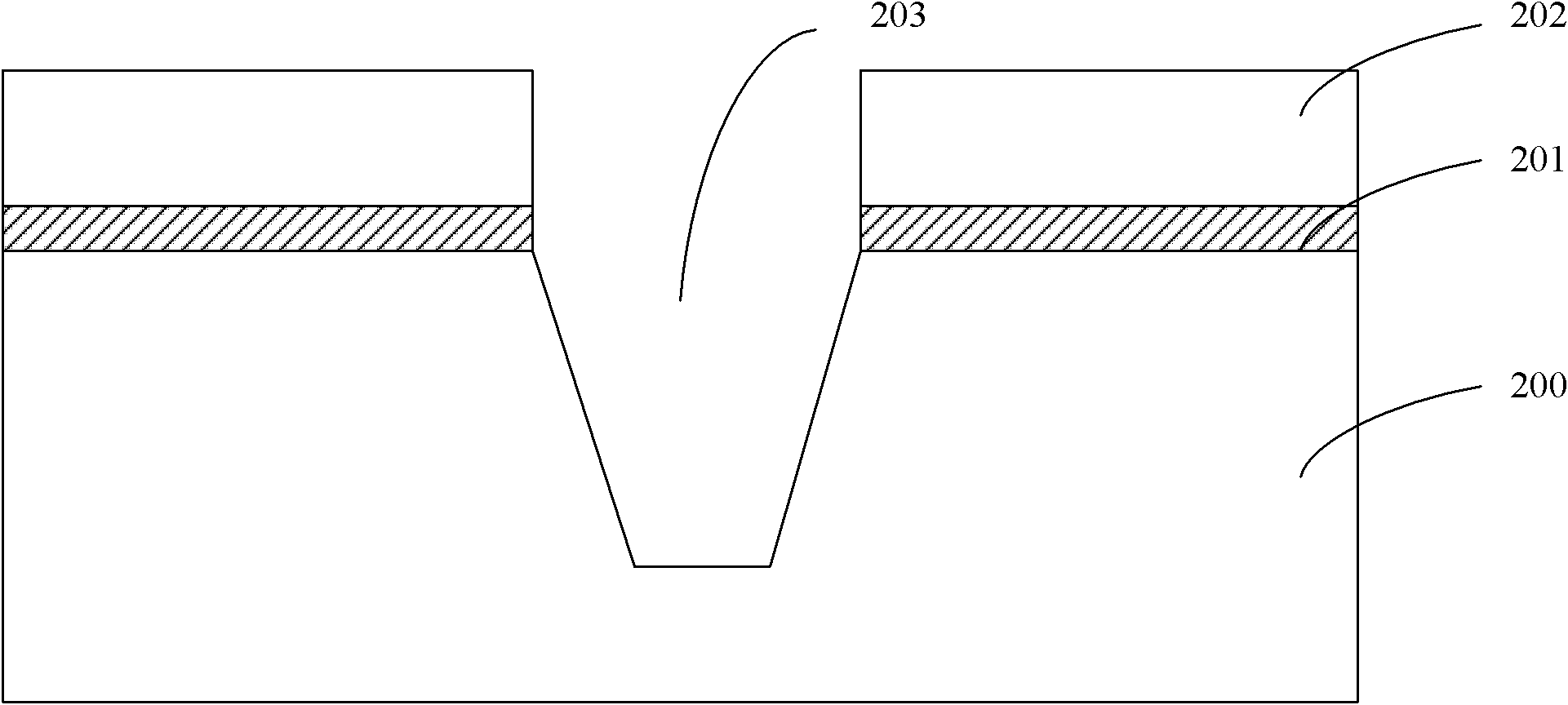

[0032] Provide a wafer with a silicon substrate, the silicon substrate can be an n-type substrate whose doping type is electron type or a p-type substrate whose doping type is hole type, combined Figure 8-14 ,Detailed description Figure 7 The shallow trench isolation manufacturing method of the present invention shown has the following steps:

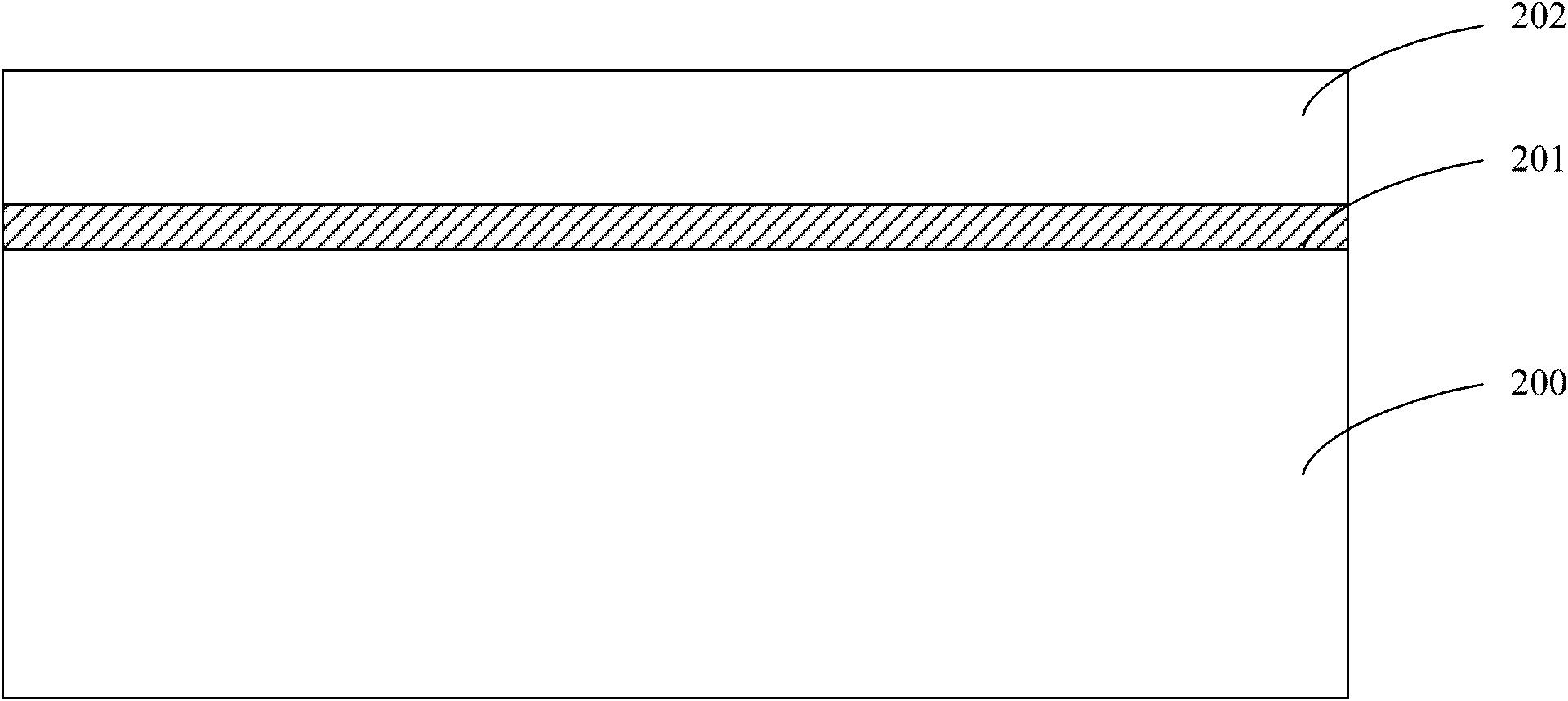

[0033] Step 701, Figure 8 It is a schematic cross-sectional structure diagram of step 701 of the STI manufacturing method in the present invention, such as Figure 8 As shown, a silicon dioxide liner 201 and a silicon nitride layer 202 are sequentially deposited on the device surface of the wafer;

[0034] In this step, the silicon dioxide liner 201 and the silicon nitride layer 202 are sequentially deposite...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com