Method for designing bonding pad of surface mounted component, bonding pad structure and printing circuit board

A technology for patch components and printed circuit boards, which is applied in the direction of printed circuits, circuits, and electrical components connected by non-printed electrical components, and can solve the problems of offset or sliding, offset or sliding of patch components. , to achieve the effect of meeting the needs of heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

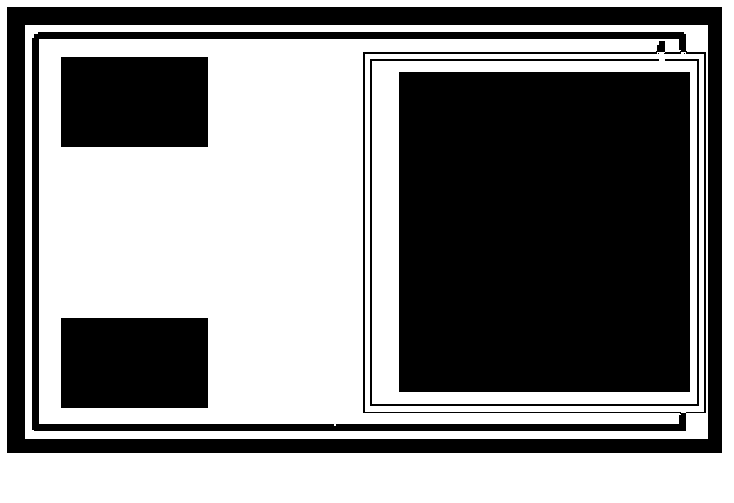

[0028] see Figure 4 , is a schematic diagram of the pad design structure of the patch component pad in Embodiment 1 of the present invention; the heat dissipation pad (pad surface layer copper) 41 is 10 × 10mm, which can be divided into 9 equal parts, and the solder resist layer of the pad after equalization (solder mask) 42 is a total of 9 pieces, and the size of each piece is: 3×3mm; the pad surface steel mesh (pastmask) 43 is a total of 9 pieces, each size is: 2.8×2.8mm; between the solder mask layer of the pad There are 40 through holes 44 in total, the diameter of each through hole is 0.3 mm, and the diameter of the pad 45 of the through holes is 0.6 mm. The size of the copper on the surface of the pad meets the electrical performance requirements and completes the signal connection; at the same time, because the area of the copper is large enough, it can effectively meet the heat dissipation requirements of the chip.

[0029] The solder resist layer 1 of the pad is d...

Embodiment 2

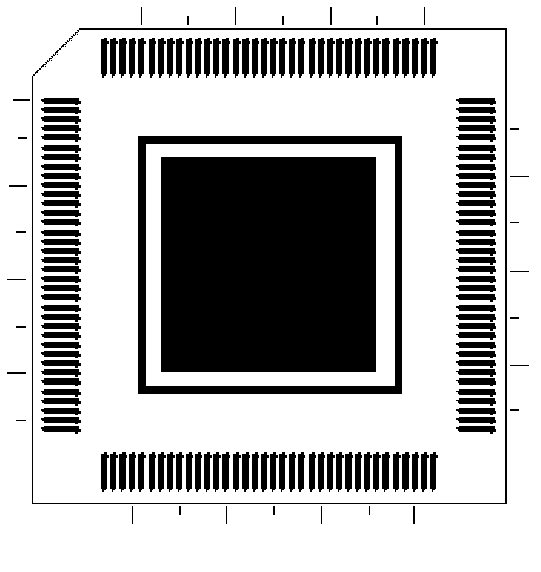

[0033] Embodiment 2 of the present invention takes a heat dissipation pad whose length×width are 18×18mm as an example, see Figure 6 , is the schematic diagram of the QFP packaging design structure after implementing the pad design method of the present invention in embodiment 2, wherein 61 is the pin welding pad around the chip component, and its pitch is 0.5mm, with 144 pins in total, and 62 is According to the size of the cooling pad of components (18×18mm), the length x width of each pad solder resist layer after equal division is 3×3mm, a total of 25 pieces, 63 for each A pad stencil corresponding to the solder mask layer of a pad, 64 is a through hole between adjacent pad solder mask layers, with a diameter of 0.5mm, and 65 is a pad with a through hole, a diameter of 0.9mm, and a total of 120 pads are used. through-hole pads. When reflow soldering, each partition of the pad of the present invention is in close contact with the cooling pin in the center of the device, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com