Parasitic PIN(positive-intrinsic negative) diode in BiCMOS(Bipolar Complementary Metal Oxide Semiconductor) process, and manufacturing method thereof

A PIN diode and process technology, applied in the field of semiconductor integrated circuit manufacturing, can solve the problems of increasing the forward conduction current of the device and increasing the cost, and achieve the effects of improving insertion loss, increasing surface area, and high isolation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment B

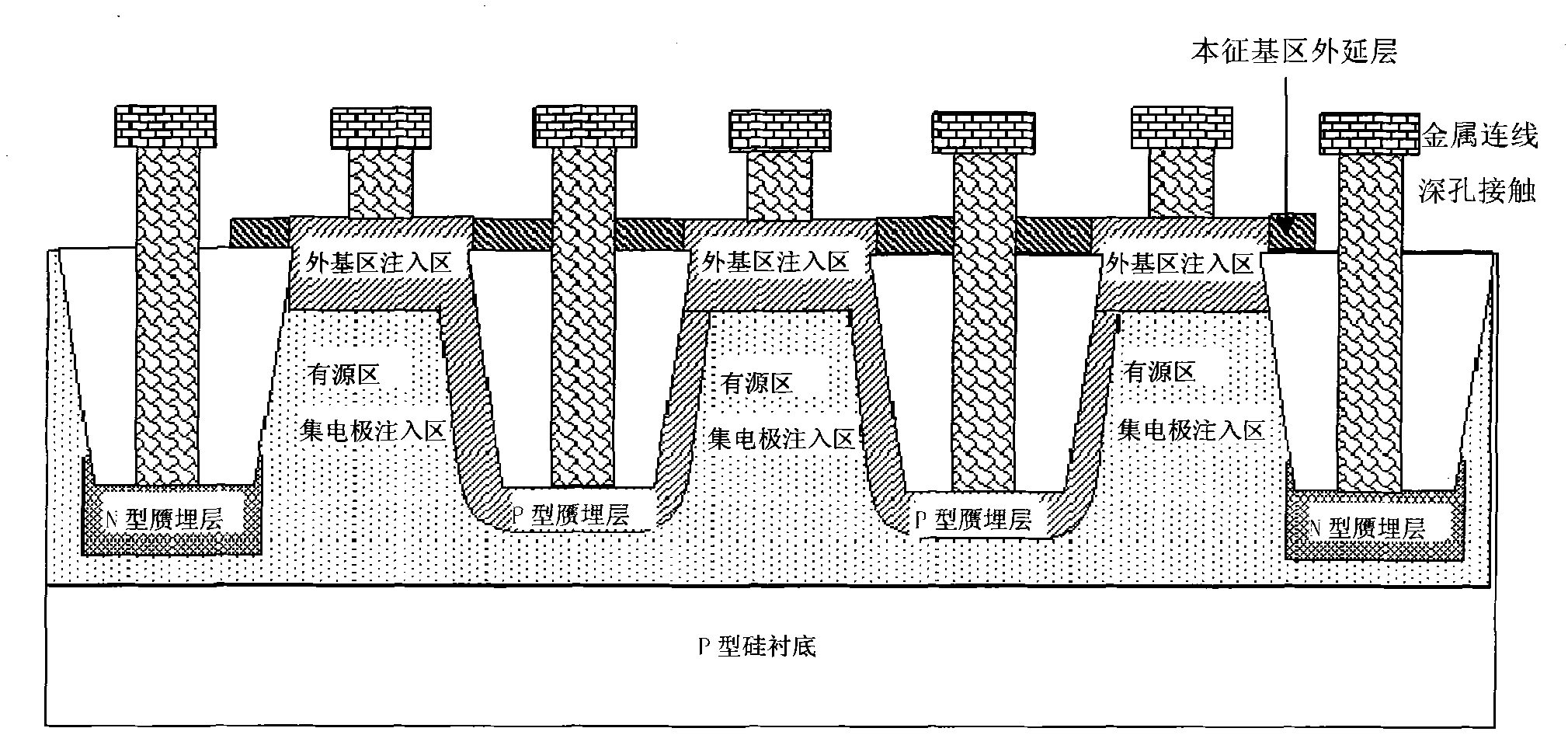

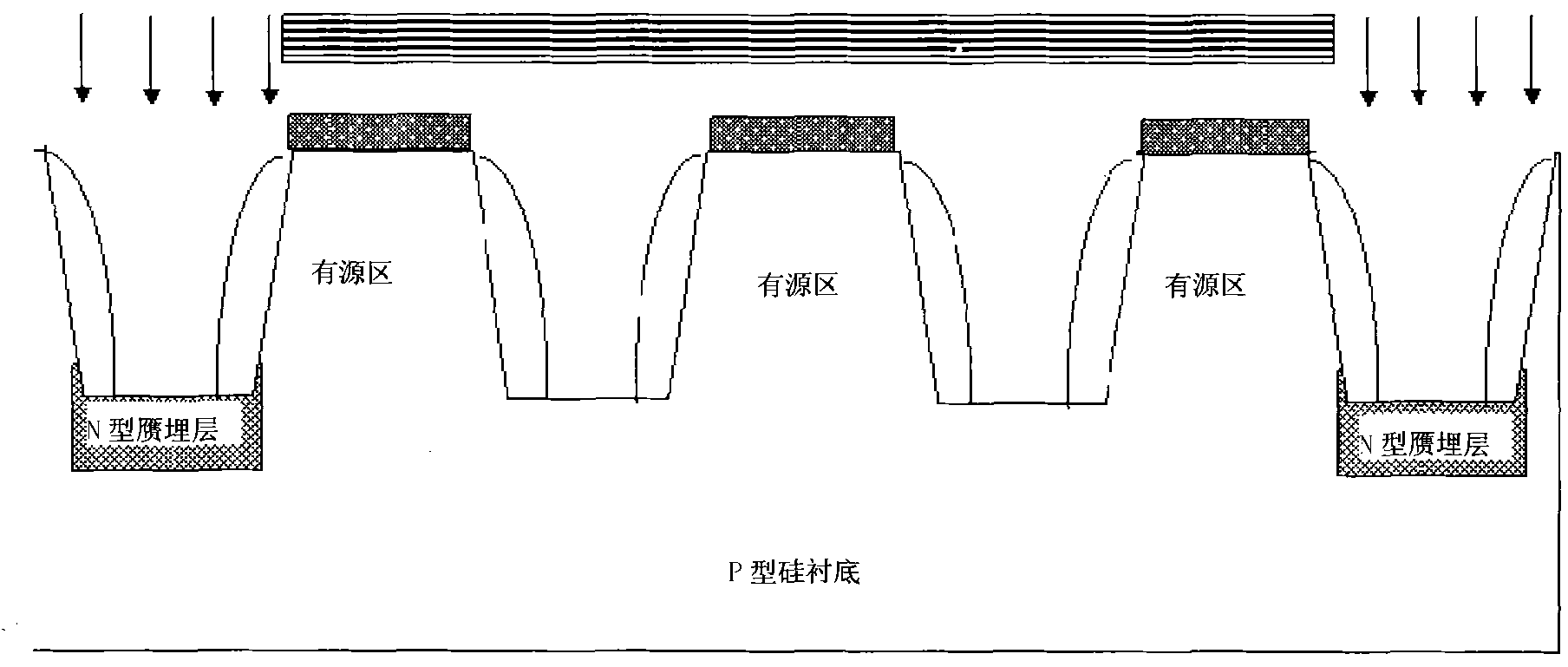

[0022] Such as figure 1 Shown is a device cross-sectional view of a parasitic PIN diode in a BiCMOS process according to an embodiment of the present invention. The parasitic PIN diode in the BiCMOS process of the embodiment of the present invention is formed on a P-type silicon substrate, and the active region is isolated by a shallow trench isolation oxide layer. The parasitic PIN diode includes: an N-type region, an I-type region and a P-type region.

[0023] The I-type region is composed of a plurality of N-type collector implanted regions formed in a plurality of adjacent active regions and connected to each other, and the depth of each of the N-type collector implanted regions is greater than that of the shallow trench isolation oxide layer The bottom of each of the N-type collector injection regions extends into the bottom of the shallow trench isolation oxide layer next to each of the N-type collector injection regions and realizes all the N-type collector injection r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com